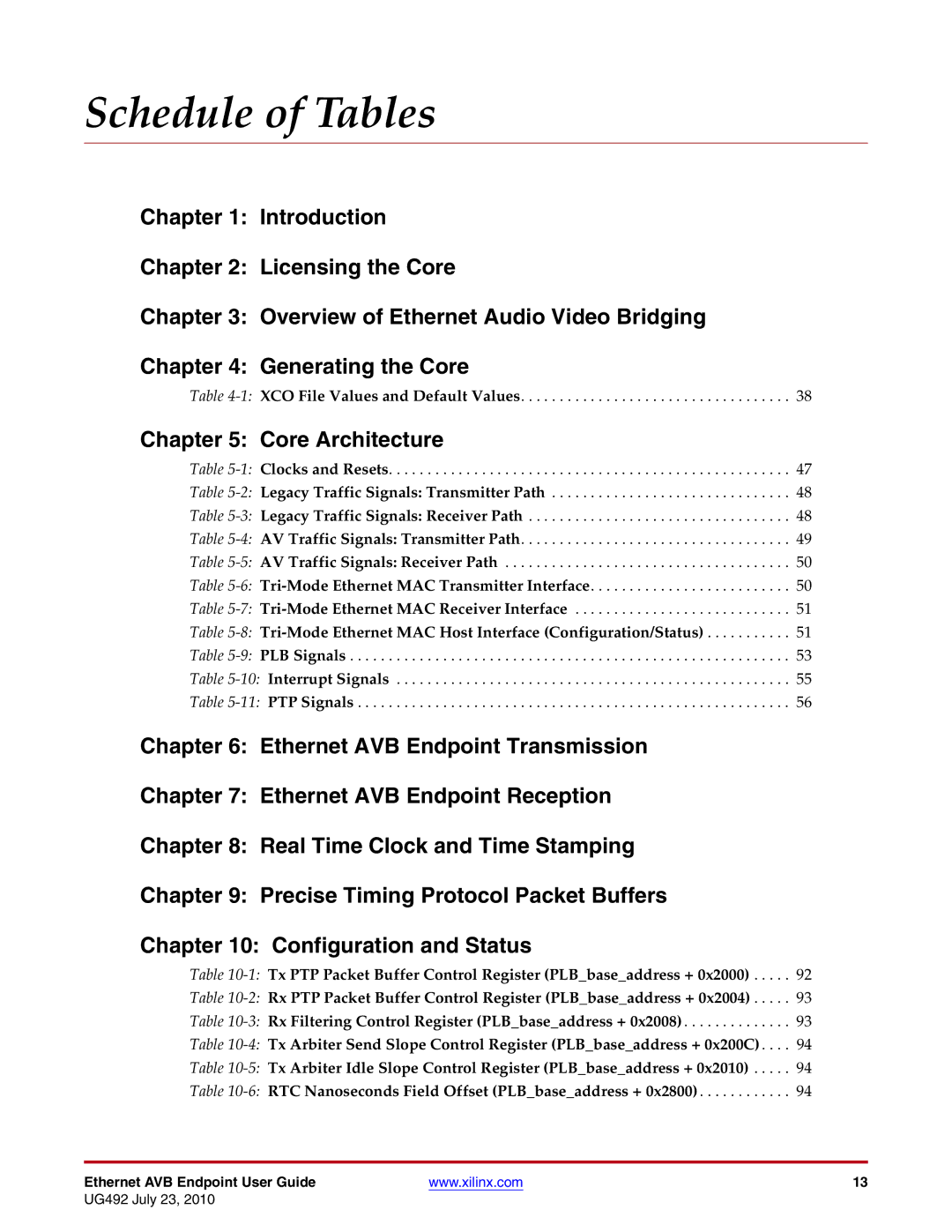

Schedule of Tables

Chapter 1: Introduction

Chapter 2: Licensing the Core

Chapter 3: Overview of Ethernet Audio Video Bridging

Chapter 4: Generating the Core

Table

Chapter 5: Core Architecture

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Chapter 6: Ethernet AVB Endpoint Transmission

Chapter 7: Ethernet AVB Endpoint Reception

Chapter 8: Real Time Clock and Time Stamping

Chapter 9: Precise Timing Protocol Packet Buffers

Chapter 10: Configuration and Status

Table

Table

Table

Table

Table

Table

Ethernet AVB Endpoint User Guide | www.xilinx.com | 13 |

UG492 July 23, 2010