Chapter 12: System Integration

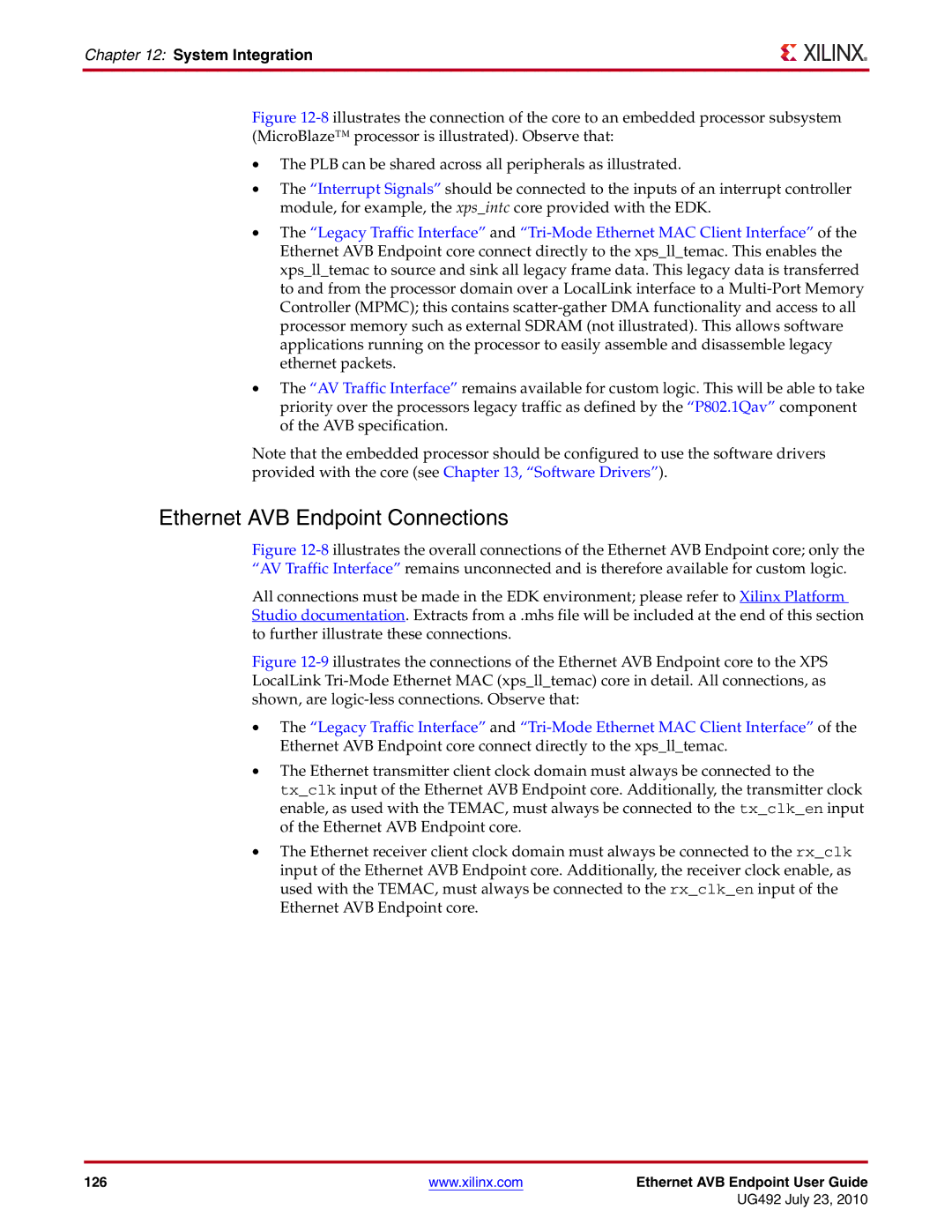

Figure 12-8 illustrates the connection of the core to an embedded processor subsystem (MicroBlaze™ processor is illustrated). Observe that:

•The PLB can be shared across all peripherals as illustrated.

•The “Interrupt Signals” should be connected to the inputs of an interrupt controller module, for example, the xps_intc core provided with the EDK.

•The “Legacy Traffic Interface” and

•The “AV Traffic Interface” remains available for custom logic. This will be able to take priority over the processors legacy traffic as defined by the “P802.1Qav” component of the AVB specification.

Note that the embedded processor should be configured to use the software drivers provided with the core (see Chapter 13, “Software Drivers”).

Ethernet AVB Endpoint Connections

Figure 12-8 illustrates the overall connections of the Ethernet AVB Endpoint core; only the “AV Traffic Interface” remains unconnected and is therefore available for custom logic.

All connections must be made in the EDK environment; please refer to Xilinx Platform Studio documentation. Extracts from a .mhs file will be included at the end of this section to further illustrate these connections.

Figure 12-9 illustrates the connections of the Ethernet AVB Endpoint core to the XPS LocalLink Tri-Mode Ethernet MAC (xps_ll_temac) core in detail. All connections, as shown, are logic-less connections. Observe that:

•The “Legacy Traffic Interface” and

•The Ethernet transmitter client clock domain must always be connected to the

tx_clk input of the Ethernet AVB Endpoint core. Additionally, the transmitter clock enable, as used with the TEMAC, must always be connected to the tx_clk_en input of the Ethernet AVB Endpoint core.

•The Ethernet receiver client clock domain must always be connected to the rx_clk input of the Ethernet AVB Endpoint core. Additionally, the receiver clock enable, as used with the TEMAC, must always be connected to the rx_clk_en input of the Ethernet AVB Endpoint core.

126 | www.xilinx.com | Ethernet AVB Endpoint User Guide |

|

| UG492 July 23, 2010 |