Core Interfaces

Interrupt Signals

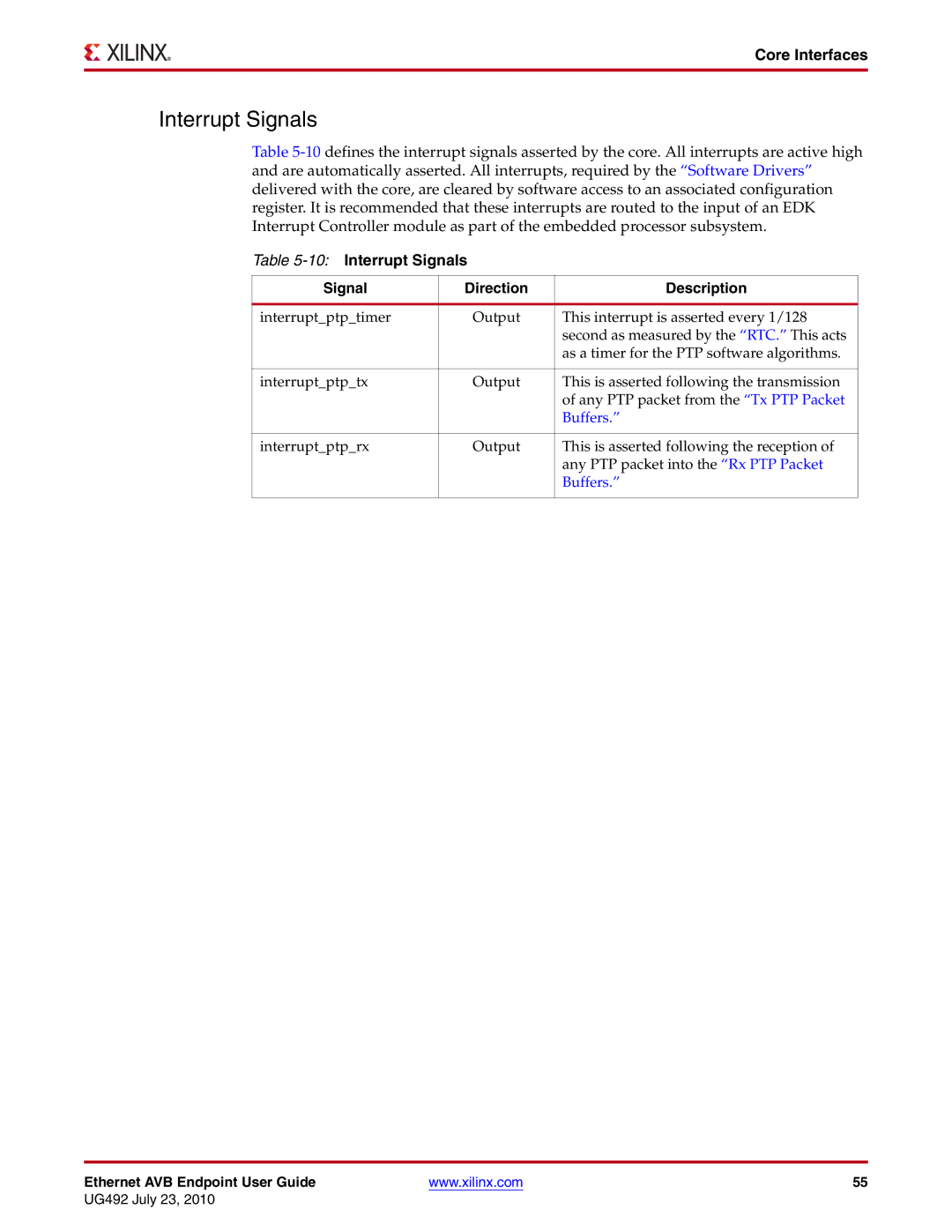

Table

Table 5-10: Interrupt Signals

Signal | Direction | Description |

|

|

|

interrupt_ptp_timer | Output | This interrupt is asserted every 1/128 |

|

| second as measured by the “RTC.” This acts |

|

| as a timer for the PTP software algorithms. |

|

|

|

interrupt_ptp_tx | Output | This is asserted following the transmission |

|

| of any PTP packet from the “Tx PTP Packet |

|

| Buffers.” |

|

|

|

interrupt_ptp_rx | Output | This is asserted following the reception of |

|

| any PTP packet into the “Rx PTP Packet |

|

| Buffers.” |

|

|

|

Ethernet AVB Endpoint User Guide | www.xilinx.com | 55 |

UG492 July 23, 2010