Ethernet AVB GUI Page 2

Ethernet AVB GUI Page 2

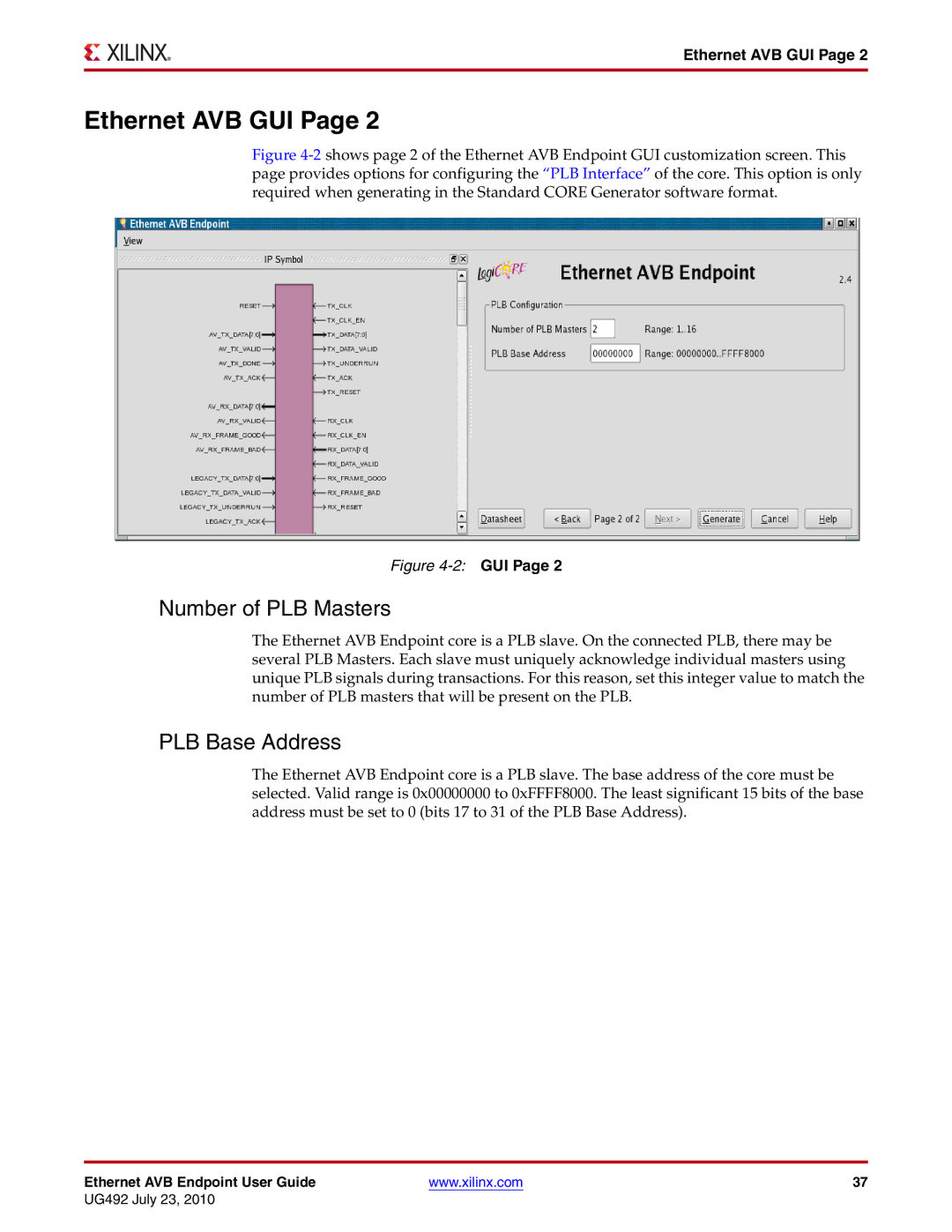

Figure 4-2 shows page 2 of the Ethernet AVB Endpoint GUI customization screen. This page provides options for configuring the “PLB Interface” of the core. This option is only required when generating in the Standard CORE Generator software format.

Figure 4-2: GUI Page 2

Number of PLB Masters

The Ethernet AVB Endpoint core is a PLB slave. On the connected PLB, there may be several PLB Masters. Each slave must uniquely acknowledge individual masters using unique PLB signals during transactions. For this reason, set this integer value to match the number of PLB masters that will be present on the PLB.

PLB Base Address

The Ethernet AVB Endpoint core is a PLB slave. The base address of the core must be selected. Valid range is 0x00000000 to 0xFFFF8000. The least significant 15 bits of the base address must be set to 0 (bits 17 to 31 of the PLB Base Address).

Ethernet AVB Endpoint User Guide | www.xilinx.com | 37 |

UG492 July 23, 2010