80386

2.11 TESTABILITY

2.11.1Self-Test

The 80386 has the capability to perform a

2.11.2 TLB Testing

The 80386 provides a mechanism for testing the Translation Lookaside Buffer (TLB) if desired. This particular mechanism is unique to the 80386 and may not be continued in the same way in future processors. When testing the TLB it is recommend- ed that paging be turned off (PG = 0 in CRO) to avoid interference with the test data being written to the TLB.

There are two TLB testing operations: 1) write en- tries into the TLB, and, 2) perform TLB lookups. Two Test Registers, shown in Figure

c:This is the command bit. For a write into TR6 to

cause an immediate write into the TLB entry, write a oto this bit. For a write into TR6 to cause an immedi- ate TLB lookup, write a 1 to this bit.

Linear Address: This is the tag field of the TLB. On a TLB write, a TLB entry is allocated to this linear address and the rest of that TLB entry is set per the value of TR7 and the value just written into TR6. On a TLB lookup, the TLB is interrogated per this value and if one and only one TLB entry matches, the rest of the fields of TR6 and TR7 are set from the match- ing TLB entry.

Physical Address: This is the data field of the TLB. On a write to the TLB, the TLB entry allocated to the linear address in TR6 is set to this value. On a TLB lookup, the data field (physical address) from the TLB is read out to here.

PL: On a TLB write, PL= 1 causes the REP field of TR7 to select which of four associative blocks of the TLB is to be written, but PL= 0 allows the internal pointer in the paging unit to select which TLB block is written. On a TLB lookup, the PL bit indicates whether the lookup was a hit (PL gets set to 1) or a miss (PL gets reset to 0).

V:The valid bit for this TLB entry. All valid bits can also be cleared by writing to CR3.

D, D#: The dirty bit for/from the TLB entry.

u, U #: The user bit for/from the TLB entry.

W, W#: The writable bit for/from the TLB entry.

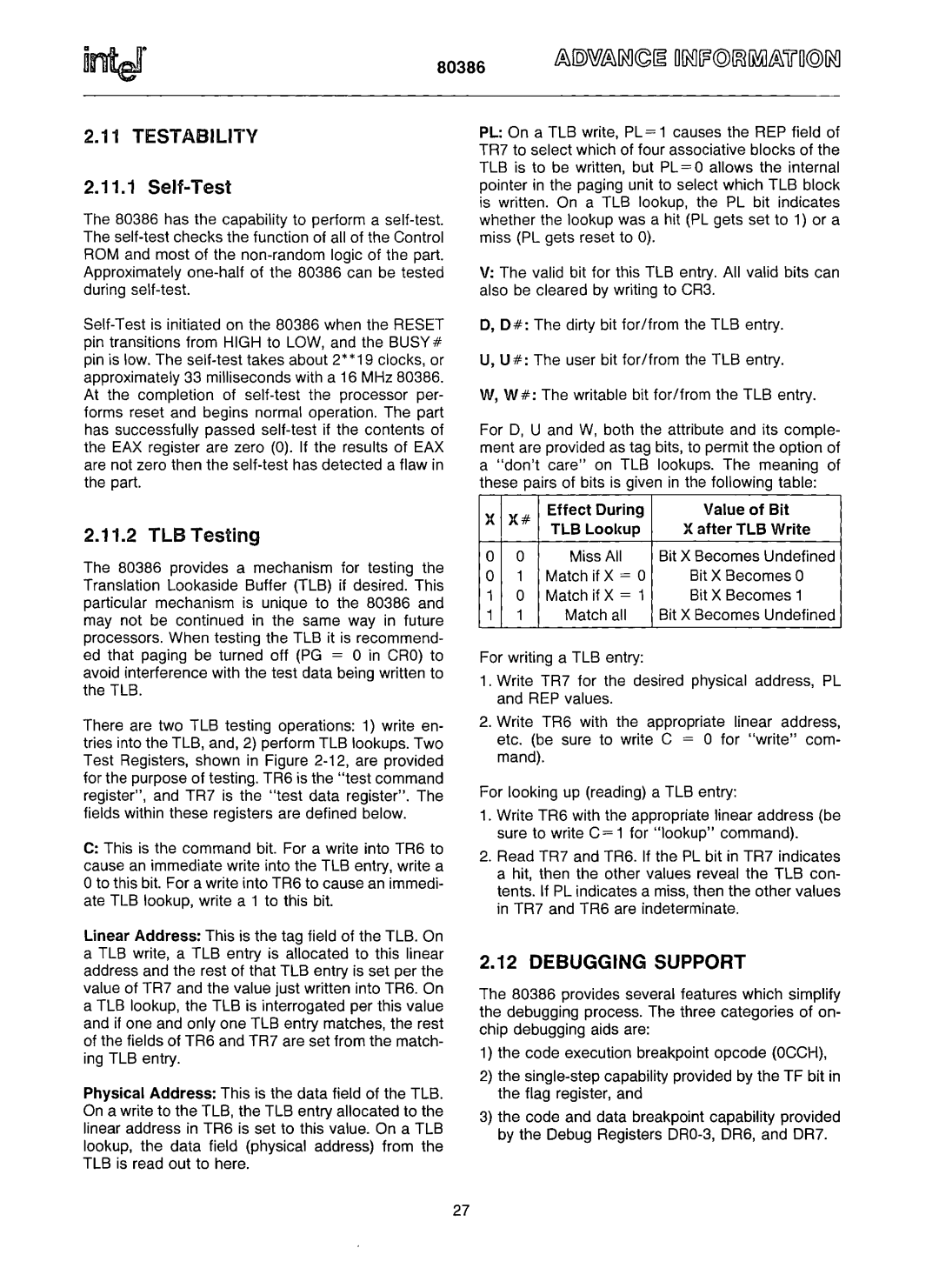

For 0, U and W, both the attribute and its comple- ment are provided as tag bits, to permit the option of a "don'tcare" on TLB lookups. The meaning of these pairs of bits is given in the following table:

)( | )(# | Effect During | Value of Bit | ||

TLB Loolcup | )( after TLB Write | ||||

|

| ||||

0 | 0 | Miss All |

| Bit X Becomes Undefined | |

0 | 1 | Match if X = | 0 | Bit X Becomes 0 | |

1 | 0 | Match if X = | 1 | Bit X Becomes 1 | |

1 | 1 | Match all |

| Bit X Becomes Undefined | |

For writing a TLB entry:

1.Write TR7 for the desired physical address, PL and REP values.

2.Write TR6 with the appropriate linear address, etc. (be sure to write C = 0 for "write" com- mand).

For looking up (reading) a TLB entry:

1.Write TR6 with the appropriate linear address (be sure to write C= 1 for "lookup" command).

2.Read TR7 and TR6. If the PL bit in TR7 indicates a hit, then the other values reveal the TLB con- tents. If PL indicates a miss, then the other values in TR7 and TR6 are indeterminate.

2.12DEBUGGING SUPPORT

The 80386 provides several features which simplify the debugging process. The three categories of on- chip debugging aids are:

1)the code execution breakpoint opcode (OCCH),

2)the

3)the code and data breakpoint capability provided by the Debug Registers

27