AMD Geode SC1200/SC1201 Processor Data Book

Publication ID 32579B

Contacts Trademarks

Advanced Micro Devices, Inc. All rights reserved

Contents

Video Processor Module

Electrical Specifications

Package Specifications

Core Logic Module

ACCESS.bus Data Transaction

Power Supply Connections

Typical Battery Configuration

Typical Battery Current Normal Operation Mode

Fast IR Timing MIR and FIR Diagram 422

Multiword DMA Data Transfer Timing Diagram 405

USB Data Signal Rise and Fall Timing Diagram 419

USB EOP Width Timing Diagram 420

427

424

425

426

32579B

Parallel Port Configuration Register

IRCP/SP3 Configuration Register

Serial Ports 1 and 2 Configuration Register

ACB1 and ACB2 Configuration Register

167

Banks 0 and 1 Common Control and Status Registers 118

119

166

F3 PCI Header Registers for Audio Configuration

Pciusb USB PCI Configuration Register Summary

F0BAR0+I/O Offset Gpio Configuration Registers

F2BAR4+I/O Offset IDE Controller Configuration Registers

404

384

400

402

SuperI/O

General Description

Video Processor

Core Logic

Video Processor Module

Features

General Features

GX1 Processor Module

SuperI/O Module

Other Features

Core Logic Module

Nand Eeprom

32579B

GX1 Module

Memory Controller

Architecture Overview 32579B

Width Memory Offset Bits Type Name/Function Reset Value

SC1200/SC1201 Processor Memory Controller Register Summary

SC1200/SC1201 Processor Memory Controller Registers

MCMEMCNTRL2 R/W

Rsvd Reserved. Write as GXBASE+840Ch-840Fh

Bit Description GXBASE+8408h-840Bh

Mcbankcfg R/W

Rsvd Reserved. Write as 0070h

Mcgbaseadd R/W

Mcdradd R/W

Mcdracc R/W

Video Input Port

Fast-PCI Bus

Display

1 GX1 Module Interface

System Reset

Clock, Timers, and Reset Logic

Reset Logic

Power-On Reset

32579B

Processor

Signal Definitions 32579B

AMD Geode

SC1200/SC1201

Jtag Interface

USB

Mnemonic Definition

Signal Definitions Legend

SC1200/SC1201

BGU481 Ball Assignment Sorted by Ball Number

Configuration

REQ0#

GNT0#

GPIO7

AFD#/DSTRB#

PAR

GPIO12

FTRDY#

AC1 IDEDATA1

Buffer1 Power Signal Name

Ball Buffer Power Signal Name

Signal Name Ball No

BGU481 Ball Assignment Sorted Alphabetically by Signal Name

FC/BE1# B17

F30

FC/BE0# D21

C11

MD26 AC29

MD23

MD24

MD25 AC28

F31

C24

N13, N14, N18

A2, A30, B2, B13

Nominal External PU/PD Strap Settings

Strap Options

Strap Options

TFT, CRT, PCI, GPIO, System

Multiplexing Configuration

Two-Signal/Group Multiplexing

Default Alternate Ball No Signal Configuration

ACCESS.bus

Internal Test

AC97 Fpci Monitoring

Three-Signal/Group Multiplexing

Gpio UART2 IDE2

Four-Signal/Group Multiplexing

Boot ROM is 16 Bits Wide. This strap signal enables

Signal Descriptions

Signal Name Ball No Type Description Mux

Maximum Core Clock Multiplier. These strap signals

Column Address Strobe. RAS#, CAS#, WE# and CKE

Memory Interface Signals

Video Port Interface Signals

4 CRT/TFT Interface Signals

Digital RGB Data to TFT

TV Interface Signals

Super Video Chrominance. S-Video chrominance sig

Current Compensation for TV DAC. a 0.1 µF to 1.2 µF

PCI Bus Interface Signals

ACCESS.bus Interface Signals

INTD# AA2

INTA#

INTB#

INTC#

BHE#

STOP#

LOCK#

DEVSEL#

REQ0#

PERR#

SERR#

REQ1#

Sub-ISA Interface Signals

Low Pin Count LPC Bus Interface Signals

IDE Interface Signals

Serial Ports UARTs Interface Signals

Universal Serial Bus USB Interface Signals

Parallel Port Interface Signals

Fast Infrared IR Port Interface Signals

Serial Bus Synchronization. This bit is asserted to syn

15 AC97 Audio Interface Signals

Power Management Interface Signals

General Purpose Wakeup I/Os. These signals each

PWRCNT2 AL7

Suspend Power Plane Control 1 and 2. Control signal

PWRBTN# AH5

PWRCNT1 AK6

Gpio Interface Signals

System Management Interrupt. This is the input to

Debug Monitoring Interface Signals

Jtag Interface Signals

Fast-PCI Bus Monitoring Signals. When enabled, this

Thermal Diode Positive / Negative. These signals are for

Test and Measurement Interface Signals

PLL6, PLL5 and PLL2 Bypass. These signals are used

Memory Internal Test Signals. These signals are used

Power and Ground Connections1

Width Offset Bits

Configuration Block Addresses

General Configuration Block Register Summary

General Configuration Block 32579B

Fpcimon

Ball # Internal Test Signals Name Add’l Dependencies

Other Signal Add’l Dependencies

PMR27

Ball # IDE Signals CRT, Gpio and TFT Signals Name

General Configuration Block

Name Add’l Dependencies

PP/ACB1/FPCI TFT/VOP

Ball # Gpio Signals LPC Signals Name Add’l Dependencies

Reserved

32579BGeneral Configuration Block

General Configuration Block

Offset 3Eh-3Fh Configuration Base Address Register CBA RO

Offset 38h Interrupt Selection Register Intsel R/W

Offset 3Dh Revision Register REV RO

Functional Description

Watchdog Timer

Usage Hints

Watchdog Registers

Watchdog Interrupt

3describes the Watchdog registers

Offset 05h-07h

High-Resolution Timer

High-Resolution Timer Registers

Watchdog Status Register Wdsts R/WC Reset Value 00h

Bit Description Offset 08h-0Bh

Reset Value xxxxxxxxh

Tmclksel Timer Clock Select

Tmen Timer Interrupt Enable

Clock Generators and PLLs

1 27 MHz Crystal Oscillator

Crystal Oscillator Circuit Components

Component Parameters Values Tolerance

Strapped Core Clock Frequency

2 GX1 Module Core Clock

Internal Fast-PCI Clock

Core Clock Frequency

SuperI/O Clocks

Core Logic Module Clocks

Video Processor Clocks

Clock Generator Configuration

Clock Registers

Clock generator and PLL registers are described in Table

66.7 MHz

1514

Reserved. Must be set to 1110

33.3 MHz

Outstanding Features

ISA

AB1C AB1D AB2C AB2D

Serial Port 3 / Infrared IR Communication Port

PC98 and Acpi Compliant

Parallel Port

Serial Port

Module Architecture

Access

Signals

Internal Internal Signals

LDN Assignments

Configuration Structure / Access

SIO Configuration Options

Index-Data Register Pair

Address Decoding

Default Configuration Setup

Standard Logical Device Configuration Registers

Standard Configuration Registers

SIO Control and Configuration Registers

Logical Device Control and Configuration Registers

Standard Configuration Registers

Index F0h-FEh Logical Device Configuration R/W

32579BSuperI/O Module

DMA Channel Select 1 R/W

SID. SIO ID

SIO Control and Configuration Registers

SIO Control and Configuration Register Map

Index Type Name Power Rail Reset Value

Relevant RTC Configuration Registers

Logical Device Control and Configuration

RTC Configuration Registers

Relevant SWC Registers

LDN 01h System Wakeup Control

Base Address MSB register

Relevant IRCP/SP3 Registers

10. IRCP/SP3 Configuration Register

LDN 03h and 08h Serial Ports 1

12. Serial Ports 1 and 2 Configuration Register

Serial Ports 1 and 2 Configuration register

11. Relevant Serial Ports 1 and 2 Registers

13. Relevant ACB1 and ACB2 Registers

14. ACB1 and ACB2 Configuration Register

LDN 05h and 06h ACCESS.bus Ports 1

ACB1 and ACB2 Configuration register

15. Relevant Parallel Port Registers

16. Parallel Port Configuration Register

17. Crystal Oscillator Circuit Components

X32I External X32O Battery = 0.1 μF

Real-Time Clock RTC

Bus Interface RTC Clock Generation

External Oscillator

Signal Parameters

External Elements

Oscillator Startup

Leap Years

Alarms

Timekeeping Data Format

Daylight Saving

Power Supply

18. System Power States

Battery-Backed RAMs and Registers

Interrupt Handling

110

Index Type Name

RTC Registers

19. RTC Register Map

20. RTC Registers

112

Index 05h Hours Alarm Register Hora R/W

Index 04h Hours Register HOR R/W

CRD is

AMD Geode SC1200/SC1201 Processor Data Book 113

Index Programmable Month Alarm Register Mona R/W

Index 0Ch RTC Control Register C CRC RO

Index Programmable Century Register CEN R/W

Parameter BCD Format Binary Format

21. Divider Chain Control / Test Selection

22. Periodic Interrupt Rate Encoding

23. BCD and Binary Formats

25. Extended RAM Map

0Eh 7Fh Battery-backed general-purpose Byte RAM

00h 7Fh Battery-backed general-purpose Byte RAM

RTC General-Purpose RAM Map 24. Standard RAM Map

System Wakeup Control SWC

Event Detection

26. Time Range Limits for Ceir Protocols

Offset Type Name Value

SWC Registers

27. Banks 0 and 1 Common Control and Status Register Map

Type Name Value

29. Banks 0 and 1 Common Control and Status Registers

30. Bank 1 Ceir Wakeup Configuration and Control Registers

Ceir Wakeup Range 2 Registers

Bit Description Ceir Wakeup Range 1 Registers

Bank 1, Offset 0Ah IRWTR1L Register R/W

Ceir Pulse Change, Range 1, High Limit

AMD Geode SC1200/SC1201 Processor Data Book 121

ACCESS.bus Interface

Data Transactions

ABD ABC

Acknowledge ACK Cycle

ABD MSB

ABC ACK

Addressing Transfer Formats

Master Mode

Acknowledge After Every Byte Rule

Arbitration on the Bus

Master Stop

Sending the Address Byte

Master Transmit

Master Receive

Configuration

Slave Mode

ACB Registers

31. ACB Register Map

32. ACB Registers

MASTER. RO

Stop Stop

Reserved Inten Interrupt Enable

Saen Slave Address Enable

EN Enable

34. Parallel Port Register Map for Second Level Offset

Legacy Functional Blocks

Parallel Port

33. Parallel Port Register Map for First Level Offset

35. Parallel Port Bit Map for First Level Offset

36. Parallel Port Bit Map for Second Level Offset

130

Type Name

Uart Functionality SP1 and SP2

41. Bank 3 Register Map

38. Bank Selection Encoding

39. Bank 1 Register Map

40. Bank 2 Register Map

Register Bits Offset

42. Bank 0 Bit Map

43. Bank 1 Bit Map

Register Bits

44. Bank 2 Bit Map

45. Bank 3 Bit Map

134

01h Register Throughout Offset 00h All Banks

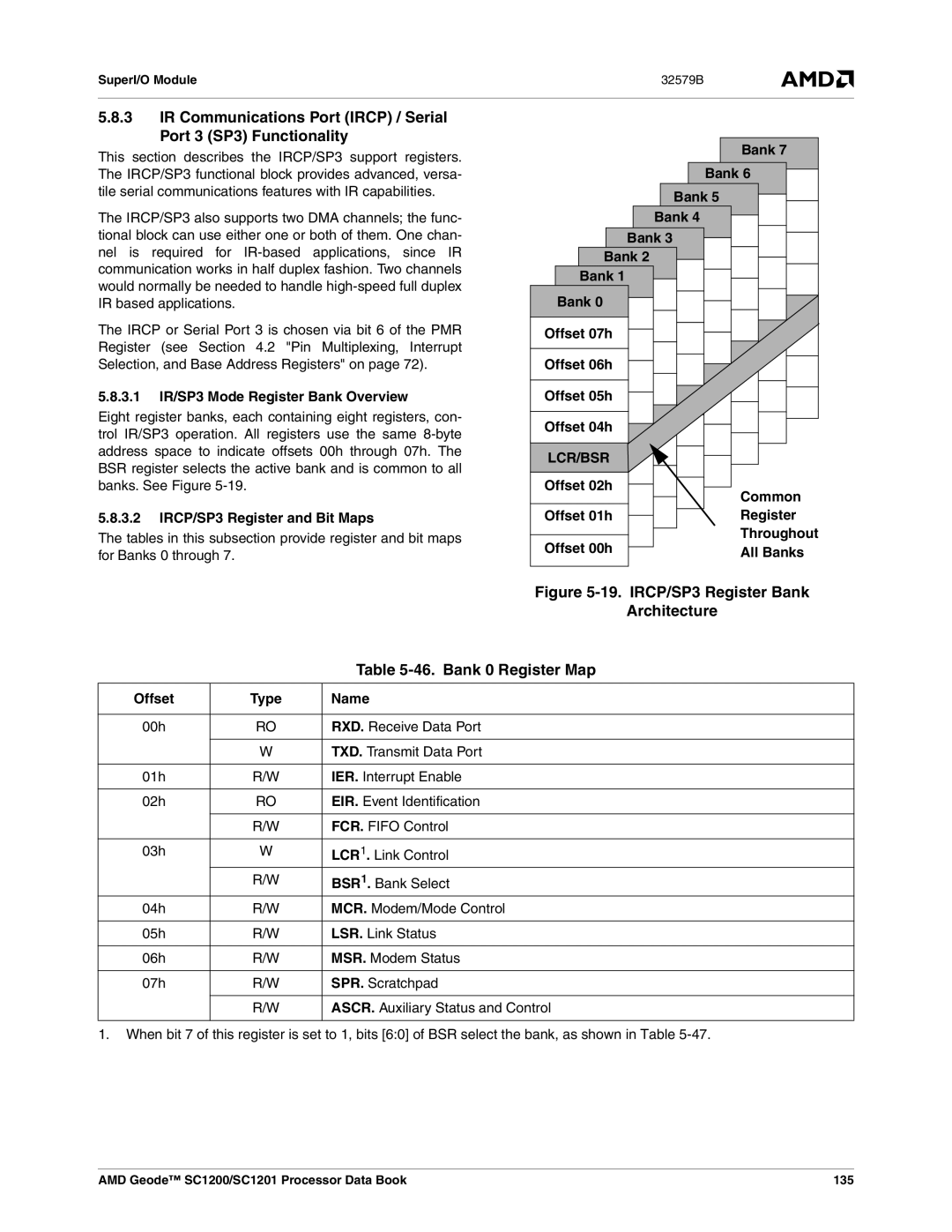

3.1 IR/SP3 Mode Register Bank Overview

46. Bank 0 Register Map

IRCP/SP3 Register and Bit Maps

BSR Bits Bank Selected Functionality

47. Bank Selection Encoding

48. Bank 1 Register Map

49. Bank 2 Register Map

50. Bank 3 Register Map

51. Bank 4 Register Map

52. Bank 5 Register Map

53. Bank 6 Register Map

54. Bank 7 Register Map

55. Bank 0 Bit Map

59. Bank 4 Bit Map

56. Bank 1 Bit Map

57. Bank 2 Bit Map

58. Bank 3 Bit Map

60. Bank 5 Bit Map

61. Bank 6 Bit Map

62. Bank 7 Bit Map

Feature List

Low Pin Count LPC Interface

Config

Integrated Audio

Video Processor Interface

Pserial Interface

Fast-PCI Interface to External PCI Bus

Video Retrace Interrupt

IDE Configuration Registers

PIO Mode

IDE Controller

Physical Region Descriptor Format

DMARDY# Strobe Ideiordy

UltraDMA/33 Signal Definitions

UltraDMA/33 Mode

Stop

Docw

Universal Serial Bus

Sub-ISA Bus Interface

IOCS0#/IOCS1#

AD310 Read AD310 Write

Sub-ISA Support of Delayed PCI Transactions

Sub-ISA Bus Cycles

Fast-PCICLK

Sub-ISA Bus Data Steering

5.4 I/O Recovery Delays

REQ# GNT#

FRAME# IRDY# TRDY# STOP# Bale ISA RD#, IOR#

ISA DMA

SD150

AD310

PCI

PCI and Sub-ISA Signal Cycle Multiplexing

Cycle Multiplexed PCI / Sub-ISA Balls

ROM Interface

DMA Channels

FRAME# TRDY#, IRDY#

ROMCS#, DOCCS# IOCS0#, IOCS1# PAR DEVSEL#,STOP#

DMA Controller

DMA Priority

DMA Transfer Modes

DMA Controller Registers

DMA Transfer Types

DMA Address Generation

Programmable Interval Timer

DMA Addressing Capability

DMA Page Registers and Extended Addressing

Mapping

PIC Interrupt Mapping

Programmable Interrupt Controller

Master

PCI Compatible Interrupts

PIC Interrupt Sequence

PIC I/O Registers

PIC Shadow Register

7.2 I/O Port 061h System Control

Fast Keyboard Gate Address 20 and CPU Reset

Keyboard Support

7.1 I/O Port 092h System Control

Power Management Logic

Wakeup Events Capability

Power Planes Control Signals vs Sleep States

Power Planes vs. Sleep/Global States

Power Management Events

AMD Geode SC1200/SC1201 Processor Data Book 161

Power Button

Power Button Override

Thermal Monitoring

Suspend Modulation

Power Management Programming

CPU Power Management

APM Support

Volt Suspend

Save-to-Disk

AMD Geode SC1200/SC1201 Processor Data Book 163

Acpi Timer Register

Peripheral Power Management

Device Idle Timers and Traps

General Purpose Timers

Power Management SMI Status Reporting Registers

Module

F1BAR0+I/O

F1BAR0+I/O

Device Power Management Programming Summary

Power Management Programming Summary

Located at F0 Index xxh Unless Otherwise Noted

Integrated Audio

Gpio Interface

Memory Region Base Address

11. Physical Region Descriptor Format

Byte

Audio Data Buffer Reserved Size

PRD3

PRD1 PRD2

Codec Gpio Status and Control Registers

Codec Configuration/Control Registers

Codec Command Register

12.2 AC97 Codec Interface

Audio SMI Related Registers

Trap SMI Enable Register

VSA Technology Support Hardware

VSA Technology

Module Core Logic Module

LPC Interface

IRQ Configuration Registers

Internal IRQ Enable Register

Internal IRQ Control Register

12. Cycle Types

PCI Configuration Space and Access Methods

13. PCI Configuration Address Register 0CF8h

Register Descriptions

Mats are found

Ter’s reset values and page references where the bit for

Register Summary

Core Logic module. Included in the tables are the regis

AMD Geode SC1200/SC1201 Processor Data Book 177

Width Reset Reference F0 Index Bits

178

32579BCore Logic Module Register Summary

F0BAR1+

15. F0BAR0 Gpio Support Registers Summary

16. F0BAR1 LPC Support Registers Summary

F0BAR0+

F1BAR0+

18. F1BAR0 SMI Status Registers Summary

20h PM2CNT PM2 Control Register 00h 21h-FFh Not Used

19. F1BAR1 Acpi Support Registers Summary

F1BAR1+

00h-03h Pcnt Processor Control Register

182

Width Reset Reference F2 Index Bits

F2BAR4+

Width Reset Reference F3 Index Bits

21. F2BAR4 IDE Controller Support Registers Summary

22. F3 PCI Header Registers for Audio Support Summary

184

Width Reset

23. F3BAR0 Audio Support Registers Summary

F3BAR0+

AMD Geode SC1200/SC1201 Processor Data Book 185

Width Reset Reference F5 Index Bits

25. F5BAR0 I/O Control Support Registers Summary

F5BAR0+

Width Reference Index Bits

26. Pciusb USB PCI Configuration Register Summary

Name Reset Value

Pciusb

27. Usbbar USB Controller Registers Summary

USBBAR0

AMD Geode SC1200/SC1201 Processor Data Book 187

28. ISA Legacy I/O Register Summary

DMA Page Registers Table

188

Keyboard Controller Registers Table

Programmable Interval Timer Registers Table

Port Type Name Reference

Programmable Interrupt Controller Registers Table

Chipset Register Space

Bridge, GPIO, and LPC Registers Function

General Remarks

AMD Geode SC1200/SC1201 Processor Data Book 191

Core Logic Module Bridge, GPIO, and LPC Registers Function

Data Parity Detected. This bit is set when

Index 09h-0Bh

316 Gpio Base Address

Index 0Eh PCI Header Type RO Reset Value 80h

Slave response

Index 0Fh PCI Bist Register RO

AMD Geode SC1200/SC1201 Processor Data Book 193

PCI Subtractive Decode

194

Reset Control Register R/W Reset Value 01h

Index 42h

Index 43h

AMD Geode SC1200/SC1201 Processor Data Book 195

Index 45h

Index 46h

Index 47h

PIT Counter 0 Enable

Reset Value 7Bh

PIT Software Reset

PIT Counter 1 Enable

ROM/AT Logic Control Register R/W Reset Value 98h

Generate SMI on A20M# Toggle

AMD Geode SC1200/SC1201 Processor Data Book 197

198

Bit Description Index 54h-59h

Index 5Ah

Index 5Bh Decode Control Register 2 R/W

INTC# Ball C9 Target Interrupt

INTB# Ball C26 Target Interrupt

INTA# Ball D26 Target Interrupt

INTD# Ball AA2 Target Interrupt

150

Index 72h

200

Chip Select 0 Positive Decode IOCS0#

Index 73h

Index 74h-75h

Index 76h

202

Ing the upper 19 bits of the incoming PCI address AD3113

Power Management Enable Register 2 R/W Reset Value 00h

Timer expires Disable Enable

AMD Geode SC1200/SC1201 Processor Data Book 203

204

AMD Geode SC1200/SC1201 Processor Data Book 205

Power Management Enable Register 3 R/W Reset Value 00h

Keyboard/Mouse Access Trap

Parallel/Serial Access Trap

206

Floppy Disk Access Trap

Primary Hard Disk Access Trap

Index 83h Power Management Enable Register 4 R/W

AMD Geode SC1200/SC1201 Processor Data Book 207

Index 84h Second Level PME/SMI Status Mirror Register 1 RO

208

AMD Geode SC1200/SC1201 Processor Data Book 209

Index 88h General Purpose Timer 1 Count Register R/W

Reserved. Always reads

210

Re-trigger General Purpose Timer 1 on Floppy Disk Activity

Second Millisecond

AMD Geode SC1200/SC1201 Processor Data Book 211

Index 8Bh General Purpose Timer 2 Control Register R/W

Index 8Dh Video Speedup Timer Count Register R/W

212

Index 8Fh-92h

Index 93h

AMD Geode SC1200/SC1201 Processor Data Book 213

214

Index 9Ah-9Bh Floppy Disk Idle Timer Count Register R/W

Index 97h

Index 98h-99h

Index A8h-A9h Video Overflow Count Register R/W

Index A6h-A7h Video Idle Timer Count Register R/W

Index B4h

Index AEh CPU Suspend Command Register WO

Index AFh Suspend Notebook Command Register WO

Index B0h-B3h

Index B9h PIC Shadow Register RO

Index BAh PIT Shadow Register RO

AMD Geode SC1200/SC1201 Processor Data Book 217

Index C0h-C3h

Index BCh Clock Stop Control Register R/W Reset Value 00h

Reserved. Set to CPU Clock Stop

Index BDh-BFh

Index CEh

Bit Description Index CCh

Mask

Index CDh

220

Index EDh-F3h

Index F4h

Index F5h Second Level PME/SMI Status Register 2 RC

AMD Geode SC1200/SC1201 Processor Data Book 221

Index F6h Second Level PME/SMI Status Register 3 RC

Index F7h Second Level PME/SMI Status Register 4 RC

Reserved. Read as

222

Index F8h-FFh

Ration registers are located. -29gives the bit formats

30. F0BAR0+I/O Offset Gpio Configuration Registers

I/O mapped registers accessed through F0BAR0

Gpio Support Registers

AMD Geode SC1200/SC1201 Processor Data Book 225

Offset 14h-17h GPDI1 Gpio Data In 1 Register RO

F0BAR0+I/O Offset 18h is set, this edge generates a PME

316 Reserved. Must be set to

010100 = GPIO20 balls A9, N31 000101

Bank

010010 = GPIO18 ball AG1 000011

010011 = GPIO19 ball C9 000100

AMD Geode SC1200/SC1201 Processor Data Book 227

Reserved. Set to

31. F0BAR1+I/O Offset LPC Interface Configuration Registers

LPC Support Registers

3121

AMD Geode SC1200/SC1201 Processor Data Book 229

230

Polarity selection

AMD Geode SC1200/SC1201 Processor Data Book 231

Reserved Serial IRQ Enable

Serial IRQ Interface Mode

Number of IRQ Data Frames

232

LPC Midi Address Select. Selects I/O Port

LPC Game Port 1 Address Select. Selects I/O Port

LPC Game Port 0 Address Select. Selects I/O Port

LPC Floppy Disk Controller Address Select. Selects I/O Port

234

Bit

32. F1 PCI Header Registers for SMI Status and Acpi Support

SMI Status and Acpi Registers Function

AMD Geode SC1200/SC1201 Processor Data Book 237

33. F1BAR0+I/O Offset SMI Status Registers

SMI Status Support Registers

Core Logic Module SMI Status and Acpi Registers Function

Suspend Modulation Enable Mirror. Read to Clear

Offset 02h-03h Top Level PME/SMI Status Register RO/RC

238

AMD Geode SC1200/SC1201 Processor Data Book 239

240

Yes To enable SMI generation, set F0 Index 82h6 =

Yes To enable SMI generation, set F0 Index 82h5 =

Offset 04h-05h

AMD Geode SC1200/SC1201 Processor Data Book 241

Offset 0Ah-1Bh

These addresses should not be written Offset 1Ch-1Fh

242

Offset 24h-27h External SMI Register R/W

3124

AMD Geode SC1200/SC1201 Processor Data Book 243

244

AMD Geode SC1200/SC1201 Processor Data Book 245

Offset 28h-4Fh Not Used Reset Value 00h

50h-FFh

246

Clkval Clock Throttling Value. CPU duty cycle

Offset 06h Smicmd OS/BIOS Requests Register R/W

34. F1BAR1+I/O Offset Acpi Support Registers

Acpi Support Registers

248

SCI generation is always enabled

1514 Reserved. Must be set to

Offset 0Ah-0Bh PM1AEN PM1A PME/SCI Enable Register R/W

1511

Offset 0Ch-0Dh PM1ACNT PM1A Control Register R/W

250

AMD Geode SC1200/SC1201 Processor Data Book 251

252

02h0

Gpwio Control Register 1 R/W Reset Value 00h

Gpwio Control Register 2 R/W Reset Value 00h Reserved

Consumer Electronic Infrared

Reserved Reset Value 00h 254

Gpwio Data Register R/W Reset Value 00h

AMD Geode SC1200/SC1201 Processor Data Book 255

Reset Value 00000F00h

Bit Description Offset 18h-1Bh

Offset 21h-FFh

IDE Controller Registers Function

AMD Geode SC1200/SC1201 Processor Data Book 257

PIOMODE. PIO mode

Core Logic Module IDE Controller Registers Function

Bit Description Index 30h-3Fh

258

Index 60h-FFh

Bit Description Index 48h-4Bh

Index 50h-53h

Index 58h-5Bh

260

IDE Controller Support Registers

Offset 0Ch-0Fh

Offset 09h

Offset 0Ah

Offset 0Bh

Audio Registers Function

37. F3 PCI Header Registers for Audio Configuration

Offset 04h-07h

38. F3BAR0+Memory Offset Audio Configuration Registers

Audio Support Registers

Core Logic Module Audio Registers Function

264

AMD Geode SC1200/SC1201 Processor Data Book 265

These bits change only on a fast write to an even address

2316

266

AMD Geode SC1200/SC1201 Processor Data Book 267

268

Mask Internal IRQ10. Write Only

Mask Internal IRQ15. Write Only

Mask Internal IRQ14. Write Only

Mask Internal IRQ11. Write Only

Reserved. Set to Assert Masked Internal IRQ12

Mask Internal IRQ4. Write Only

Mask Internal IRQ3. Write Only

Assert Masked Internal IRQ14

AMD Geode SC1200/SC1201 Processor Data Book 271

Bit Description Assert Masked Internal IRQ1

Offset 2Ch-2Fh

Audio Bus Master 1 Command Register R/W Reset Value 00h

Offset 29h Audio Bus Master 1 SMI Status Register RC

Offset 2Ah-2Bh

Offset 34h-37h

Audio Bus Master 2 Command Register R/W Reset Value 00h

Offset 31h Audio Bus Master 2 SMI Status Register RC

Offset 32h-33h

Offset 3Ch-3Fh

Audio Bus Master 3 Command Register R/W Reset Value 00h

Offset 39h Audio Bus Master 3 SMI Status Register RC

Offset 3Ah-3Bh

Offset 44h-47h

Audio Bus Master 4 Command Register R/W Reset Value 00h

Offset 41h Audio Bus Master 4 SMI Status Register RC

Offset 42h-43h

Offset 4Ch-4Fh

Audio Bus Master 5 Command Register R/W Reset Value 00h

Offset 49h Audio Bus Master 5 SMI Status Register RC

Offset 4Ah-4Bh

39. F5 PCI Header Registers for X-Bus Expansion

Bus Expansion Interface Function

Index 28h-2Bh

Bit Description Index 1Ch-1Fh

Index 20h-23h

Index 24h-27h

Index 50h-53h F5BAR4 Mask Address Register R/W

Index 58h F5BARx Initialized Register R/W Reset Value 00h

Index 48h-4Bh F5BAR2 Mask Address Register R/W

Index 4Ch-4Fh F5BAR3 Mask Address Register R/W

Bit Description Index 64h-67h

Index 68h-FFh

280

40. F5BAR0+I/O Offset X-Bus Expansion Registers

Bus Expansion Support Registers

F5 Index 10h, Base Address Register 0 F5BAR0 set

282

Three USB transceivers. Default = 128

USB transceivers. Default =

Iotestporten Debug Test Port Enable

AMD Geode SC1200/SC1201 Processor Data Book 283

41. Pciusb USB PCI Configuration Registers

USB Controller Registers Pciusb

Core Logic Module USB Controller Registers Pciusb

Reserved. Must be set to Index 08h

Reset Value 08h

Index 0Dh Latency Timer Register R/W

Bit Description Index 06h-07h Status Register R/W

42. USBBAR+Memory Offset USB Controller Registers

286

32579BCore Logic Module USB Controller Registers Pciusb

FrameNumberOverflowEnable

HcInterruptEnable Register R/W Reset Value = 00000000h

OwnershipChangeEnable

RootHubStatusChangeEnable

Offset 28h-2Bh

Bit Description StartOfFrameEnable

Offset 20h-23h

Offset 24h-27h

Reserved. Read 0s

Reset Value = 00000628h

Reset Value = 01000003h

Bit Description Offset 38h-3Bh HcFrameRemaining Register RO

3018

BalPower

Read LocalPowerStatusChange. Not supported. Always read

Offset 50h-53h HcRhStatus Register R/W

AMD Geode SC1200/SC1201 Processor Data Book 291

HcRhPortStatus1 Register R/W Reset Value = 00000000h

Read PortResetStatus

Read PortSuspendStatus

Read PortEnableStatus

Read CurrentConnectStatus

292

AMD Geode SC1200/SC1201 Processor Data Book 293

Reserved Reset Value = xxh 294

AMD Geode SC1200/SC1201 Processor Data Book 295

43. DMA Channel Control Registers

ISA Legacy Register Space

Write

Priority Mode

Timing Mode

Core Logic Module ISA Legacy Register Space

Bit Description Port 00Bh

Transfer Mode

Channel Number Mode Select

32579BCore Logic Module ISA Legacy Register Space

Write DMA Command Register, Channels

Undefined

AMD Geode SC1200/SC1201 Processor Data Book 299

Port 0D8h

Bit Description Port 0D2h

Port 0D4h

Port 0D6h

44. DMA Page Registers

45. Programmable Interval Timer Registers

Port 043h R/W

Current Counter Mode BCD Mode

Bit Description Port 042h Write

Counter Value Read

46. Programmable Interrupt Controller Registers

IRQ0 / IRQ8 Mask

Poll Command

Register Read Mode

Bit Description IRQ1 / IRQ9 Mask

IRQ4 / IRQ12 In-Service

Interrupt Service Register IRQ7 / IRQ15 In-Service

IRQ6 / IRQ14 In-Service

IRQ5 / IRQ13 In-Service

47. Keyboard Controller Registers

49. Miscellaneous Registers

48. Real-Time Clock Registers

AMD Geode SC1200/SC1201 Processor Data Book 309

310

Graphics-Video Overlay and Blending

General Features

Video Input Port VIP Interface

Hardware Video Acceleration

Tvout

Display Modes

Video Input Port

VIP

Video Processor Module

Functional Description

Video Support

VBI Support

Active Video

Video Input Port VIP

Direct Mode and Capture Mode Configurations

Bob

Address not changed during runtime

AMD Geode SC1200/SC1201 Processor Data Book 317

Weave

Capture VBI Mode

Ping-pongs between the two buffers during runtime

AMD Geode SC1200/SC1201 Processor Data Book 319

320

Video Block

Video Input Formatter

Line Buffer

Maintaining Aspect Ratio

Horizontal Downscaler with 4-Tap Filtering

Filtering

Horizontal Downscaler

Ai,j Ai,j+1 Ai+1,jAi+1,j+1

Line Buffers

Formatter

2.5 2-Tap Vertical and Horizontal Upscalers

RAM

Mixer/Blender Block

CSC

RGB

324

Valid Mixing/Blending Configurations

Filter2 Bit Mode Comment

Flicker

3.4 1/2 Y Flicker Filter

YUV to RGB CSC in Video Data Path

Gamma Correction

RGB to YUV CSC

Alpha Windows

Graphics Window

Video Window

Cursor Window

CHROMASEL1

Truth Table for Alpha Blending

Mixing/Blending Operation

Color

328

Vesa

Flicker Filter, Interlaced Video YUV Mixing/Blending Mode

Tvout Block

Flicker Filter and Scan Rate Conversion

Integrated DACs

Vesa DDSC2B and Dpms Support

T1 is a programmable multiple of frame time T0+T1

Power Sequence

TFT Interface

HSYNC, VSYNC, TFTDE, Tftdck

332

Divider Phase Charge Loop

Integrated PLL

Compare Pump Filter Divider Out

F4BAR0 Video Processor Configuration Registers Summary

F4 PCI Header Registers for Video Processor Support Summary

F4BAR0+

334

32579BVideo Processor Module Register Summary

F4BAR2+

Name Value Tvout Configuration Registers

F4BAR2 VIP Support Registers Summary

Encoder Registers

3112 VIP Base Address 110 Address Range. Read Only

Reset Value 0504h

Reset Value 030000h

Video Processor Registers Function

Video Processor Module Video Processor Registers Function

Index 3Eh-FFh Reserved

AMD Geode SC1200/SC1201 Processor Data Book 337

To 0 or 1 should be written with a value that is read

Video Configuration Register R/W Reset Value 00000000h

EN42X Enable 42x Format. Allows format selection

Video Processor Support Registers F4BAR0

Ddcsdaout DDC Output Data. DDC data bit for output

Offset 04h-07h Display Configuration Register R/W

Tions of the power sequence control lines 1614

3028

340

Offset 08h-0Bh Video X Position Register R/W

AMD Geode SC1200/SC1201 Processor Data Book 341

Bit Description 100

Block Offset 20h-23h

Reset Value 00001400h

12 PLL2PWREN PLL2 Power-Down Enable

Bit Description Offset 1Ch-1Fh

FLTCO3 Filter Coefficient 3. For the tap-3 filter

DTS Downscale Type Select

Offset 40h-43h Video Downscaler Coefficient Register R/W

FLTCO4 Filter Coefficient 4. For the tap-4 filter

Bit Description Offset 44h-47h CRC Signature Register R/W

Reserved Signen Signature Enable

Reset Value 0000xxxxh

Reset Value 00060000h

AMD Geode SC1200/SC1201 Processor Data Book 345

100 i.e., shift one line otherwise, leave at

346

Bit Description Offset 50h-53h

Offset 54h-57h

Offset 60h-63h Alpha Window 1 X Position Register R/W

3118

Decremented until it is reloaded via bit 17 Loadalpha

AMD Geode SC1200/SC1201 Processor Data Book 347

348

Video Fifo Underflow Empty

Offset 90h-93h

Offset 94h-97h

Offset 400h-403h

Upscale horizontally VBI data by

Video Fifo OverFlow Full

VBI Fifo Underflow Empty

VBI Fifo Overflow Full

Port Offset 41Ch-41Fh

Genlocktouten GenLock Timeout Enable

Bit Description Offset 414h-417h

3120 Reserved 190

3121 Reserved 200

Ctgenlocken Enable Continuous GenLock Function

Sggenlocken Enable a Single GenLock Function

Offset 424h-427h

Offset 810h-813h

Bit Description Offset 80Ch-80Fh

Offset C00h-C03h

Horintp Horizontal Interpolation

Fieldinvr Field Invert

Offset 81Ch-81Fh

AMD Geode SC1200/SC1201 Processor Data Book 355

2920

D24 A24

TV DAC Mode Bits Ball No

A23 Mode

Offset C08h-C0Bh

AMD Geode SC1200/SC1201 Processor Data Book 357

Offset C24h-C27h

3114

Offset C28h-C2Bh

Offset C50h-C53h

Reset Value 00000020h

Reset Value 00000004h

Bit Description Offset C2Ch-C2Fh

AMD Geode SC1200/SC1201 Processor Data Book 359

10. F4BAR2+Memory Offset VIP Configuration Registers

VIP Support Registers F4BAR2

All other decodes Reserved

2322

Capture Store to Memory VBI Data

Capture Store to Memory Video Data

Reserved.Read Only Current Field. Read Only

Offset 24h-27h Video Data Even Base Register R/W

Video Data Capture Active. Read Only

Reserved. Read Only Run Status. Read Only

Offset 14h-17h

Offset 48h-4Bh VBI Data Pitch Register R/W

3116 Reserved 150

Offset 2Ch-3Fh

Offset 44h-47h VBI Data Even Base Register R/W

Optional Instruction Support

Jtag Mode Instruction Support

Testability Jtag

Mandatory Instruction Support

364

Absolute Maximum Ratings

General Specifications

Power/Ground Connections and Decoupling

Electro Static Discharge ESD

Symbol Parameter Min Typ Max Unit Comments

Operating Conditions

366

DC Current

Power Planes of External Interface Signals

Power Plane Signal Names VCC Balls VSS Balls

Power State Parameter Definitions

DC Characteristics for On State

Ball Capacitance and Inductance

DC Characteristics for Active Idle, Sleep, and Off States

Symbol Parameter Note Min Typ Max Unit Comments

Symbol Parameter Min Typ Max Unit Comment

External PU or PD resistor

Pull-Up and Pull-Down Resistors

Balls with PU/PD Resistors

VIO

10. Buffer Types

DC Characteristics

Symbol Description Reference

Wire

Inab DC Characteristics

Inbtn DC Characteristics

Inpci DC Characteristics

INTS1 DC Characteristics

Instrp DC Characteristics

INT DC Characteristics

Ints DC Characteristics

ODn DC Characteristics

Inusb DC Characteristics

Ousb DC Characteristics

Odpci DC Characteristics

Op/n DC Characteristics

Opci DC Characteristics

CLK

AC Characteristics

11. Default Levels for Measurement Switching Parameters

Symbol Parameter Value

Memory Controller Interface

Outputs

Inputs

13.5

32579BElectrical Specifications

12. Memory Controller Timing Parameters

SDCLK30, Sdclkout high time

MD630 Data Valid Read Data

T1, t2, t3 t10

SDCLK30 Control Output, MA120

BA10, MD630

Vpckin Vref

14. Video Output Port Timing Parameters

15. TFT Timing Parameters

CRT and TFT Interface

16. CRT Vesa Compatible DAC RED, GREEN, and Blue Outputs

Symbol Parameter Note Min Max Unit Comments

LSB Tvref

RES

IRE

LSB DNL

ACCESS.bus Interface

18. ACCESS.bus Input Timing Parameters

19. ACCESS.bus Output Timing Parameters

AB1C AB2C

AB1D AB2D

AB1D AB2D AB1C AB2C

AB1D AB2D AB1C

AMD Geode SC1200/SC1201 Processor Data Book 387

PCI Bus

20. PCI AC Specifications

Equation a Equation B

64VIO

Pciclk 0.4 V IO

21. PCI Clock Parameters

22. PCI Timing Parameters

Symbol Value Unit Comments

23. Measurement Condition Parameters

Measurement and Test Conditions

Ms typ

Power

Signals

Input Valid

Bus Width Min

Symbol Parameter Bits Type Comments

Sub-ISA Interface

24. Sub-ISA Timing Parameters

MEMR#/DOCR#/IOR#

Bus Width Min Max Symbol Parameter Bits Type Comments

IOW#/WR# MEMW#/DOCW#

ROMCS#/DOCCS#

IOR#/RD#/TRDE#

MEMR#/DOCR#

D150

DOCCS#/ROMCS#

IOCS10#

IOW#/WR# MEMW#/DOCW# TRDE#

LPC Interface 25. LPC and Serirq

IDERST# pulse width

IDE signals fall time from 0.9V IO to 0.1V IO = 40 pF

IDE signals rise time from 0.1V IO to 0.9V IO = 40 pF

IDE Interface Timing 26. IDE General Timing Parameters

Width 8-bit min

Mode Symbol Parameter Unit Comments

27. IDE Register Transfer to/from Device Timing Parameters

Cycle time min

IDEIORDY0 2,3

Addr valid1

IDEIOR0# IDEIOW0# Write IDEDATA70

Read IDEDATA70

28. IDE PIO Data Transfer to/from Device Timing Parameters

165 125 100

402

IDEIOR0# IDEIOW0# Write IDEDATA150

Read IDEDATA150

AMD Geode SC1200/SC1201 Processor Data Book 403

29. IDE Multiword DMA Data Transfer Timing Parameters

IDECS10#

IDEDREQ0 IDEDACK0# IDEIOR0# IDEIOW0#

AMD Geode SC1200/SC1201 Processor Data Book 405

Mode Symbol Parameter Min Max Unit Comments

30. IDE UltraDMA Data Burst Timing Parameters

406

IDEIRDY0 DSTROBE0

IDEREQ0

STOP0

IDEIOR0# HDMARDY0#

408

IDEIRDY0 DSTROBE0 at device

IDEDATA150 at device IDEIRDY0 DSTROBE0 at host

IDEDATA150 at host

AMD Geode SC1200/SC1201 Processor Data Book 409

IDEDREQ0 device IDEDACK0# host

IDEIOW0#STOP0# host

IDEIOR0#HDMARDY0#

IDEDREQ0 device

IDEIOW0# STOP0#

410

IDEADDR20

IDEIOW0# STOP0# host IDEIOR0# HDMARDY0# host

IDEIRDY0 DSTROBE0 device IDEDATA150 device

IDECS01#

IDEIOR0# HSTROBE0# host

DevicetUI IDEDACK0# host

IDEIOW0# STOP0# host

IDEIORDY0 DDMARDY0 device

IDEDATA150 at device

HSTROBE0#

At host

IDEDATA150 At host IDEIOR0# HSTROBE0# at device

414

IDEDREQ0 device IDEDACK0# host IDEIOW0# STOP0# host

IDEIORDY0# DDMARDY0#

IDEIOR0# HSTROBE0#

AMD Geode SC1200/SC1201 Processor Data Book 415

IDEIORDY0# DDMARDY0# device

IDEDATA150 host IDEADDR20 IDECS01#

IDEDACK0# host

IDEDREQ0 device IDEDACK0 host IDEIOW0# STOP0# host

IDEDATA150 host IDECS01# IDEADDR20

416

Universal Serial Bus USB 31. USB Timing Parameters

Full Speed Receiver EOP Width Note

Low Speed Source Note

Low Speed Receiver EOP Width Note

Source EOP width

Host upstream

Receiver data jitter tolerance for paired

Consecutive Transitions

Rise Time Fall Time

Differential Data Lines

Differential Data Lines Crossover Points 2.0

Differential Crossover Points Data Lines

Differential Data to SE0 Skew

Data Crossover Level

EOP Width

Setting of the Rxhsc bit bit 5 of the Rccfg register

Modulation signal period

TCPN + Transmitter Sharp-IR and Consumer Remote Control

SIR signal pulse width

Fast IR Port Timing 33. Fast IR Port Timing Parameters

MIR

FIR

STB#

Busy ACK#

Symbol Parameter Min

35. Enhanced Parallel Port Timing Parameters

Unit Comments

Busy

36. ECP Forward Mode Timing Parameters

Extended Capabilities Port ECP Timing

AFD#

BUSY#

37. ECP Reverse Mode Timing Parameters

AC97RST# active low pulse width

Audio Interface Timing AC97 38. AC Reset Timing Parameters

AC97RST# inactive to Bitclk 162.8 Startup delay

Sync inactive to Bitclk startup 162.8 Delay

AC97CLK Vold

40. AC97 Clocks Parameters

SDATAOUT/SYNC SDATAIN, SDATAIN2

41. AC97 I/O Timing Parameters

42. AC97 Signal Rise and Fall Timing Parameters

Bitclk Sdataout

43. AC97 Low Power Mode Timing Parameters

End of Slot 2 to Bitclk Sdatain low

Slot

ONCTL# PWRBTN#

Power Management

Power management event to ONCTL# Assertion

44. PWRBTN# Timing Parameters

PWRBTN# ONTCL# PWRCNT21 POR#

434

POR# 32KHZ

TDI, TMS hold time

TDI, TMS setup time

Non-test inputs setup time

Jtag Interface 48. Jtag Timing Parameters

436

Output Signals

Input Signals

TDI TMS TDO

Thermal Characteristics

ΘJC ×C/W

Case-to-Ambient Thermal Resistance Example @ 85C

Assume P max = 9W and TA max = 40C Therefore

Heatsink Considerations

Example

Assume P max = 5W and TA max = 40C Therefore

Physical Dimensions

Package Specifications

AMD Geode SC1200/SC1201 Processor Data Book 439

440

BGU481 Package Bottom View

MHz

Order Information

Macrovision Product Notice

Ordering Part Number Core Frequency

Data Book Revision History

Table A-1. Revision History

Revision # Revisions / Comments