DFX-8500

2.3.8 Plunger Drive Circuit

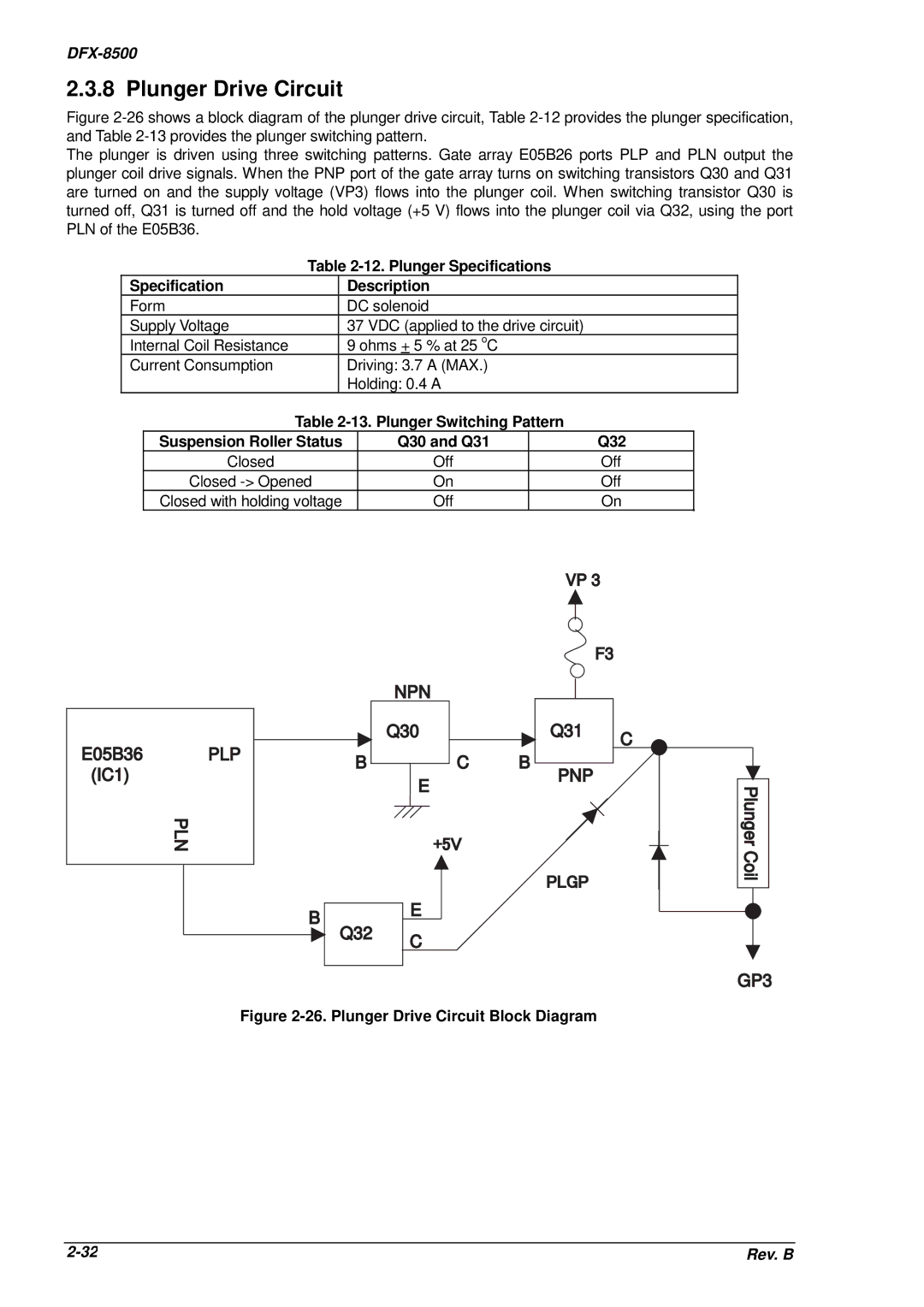

Figure 2-26 shows a block diagram of the plunger drive circuit, Table 2-12 provides the plunger specification, and Table 2-13 provides the plunger switching pattern.

The plunger is driven using three switching patterns. Gate array E05B26 ports PLP and PLN output the plunger coil drive signals. When the PNP port of the gate array turns on switching transistors Q30 and Q31 are turned on and the supply voltage (VP3) flows into the plunger coil. When switching transistor Q30 is turned off, Q31 is turned off and the hold voltage (+5 V) flows into the plunger coil via Q32, using the port PLN of the E05B36.

| Table | |

Specification |

| Description |

Form |

| DC solenoid |

Supply Voltage |

| 37 VDC (applied to the drive circuit) |

Internal Coil Resistance |

| 9 ohms + 5 % at 25 oC |

Current Consumption |

| Driving: 3.7 A (MAX.) |

|

| Holding: 0.4 A |

Table

Suspension Roller Status | Q30 and Q31 | Q32 |

Closed | Off | Off |

Closed | On | Off |

Closed with holding voltage | Off | On |

VP 3

F3

NPN

E05B36 PLP (IC1)

PLN

B

Q30

B

E

| E | |

Q32 | ||

C | ||

| ||

|

|

CB

Q31

PNP

C

Plunger Coil

GP3

Figure 2-26. Plunger Drive Circuit Block Diagram

Rev. B |