MN101C77C/F77G LSI User’s Manual

Page

Page

Summary

Precautions and warnings

Subtitle Sub-subtitle

Main text Key information

„Finding Desired Information

Page

Page

Contents

Chapter

Chapter Ports

Chapter Prescaler

Chapter Bit Timer

Chapter Watchdog Timer

Serial Interface

Automatic Transfer Controller

Chapter Appendices

18-4 Reprogramming Flow

Page

Chapter Overview

Product Summary

Overview

Overview

Product Summary

KB Flash version 6 KB

Hardware Functions

CPU Core MN101C Core

KB Flash version 128 KB

External interrupts with/without noise filter

Timers Timers 6 can operate independently

Timer 0 8-Bit timer for general use

Timer 1 8-Bit timer for general use

Timer 7 16-Bit timer for general use

Timer 4 8-Bit timer for general use or Uart baud rate timer

Timer 5 8-Bit timer for general use or Uart baud rate timer

‰ Time base timer

Buzzer output

Watchdog timer

Remote control output

Full-Duplex Uart Baud rate timer Timer

Serial interface 4 Slave IIC ‰ IIC slave serial interface

LED driver Pins Port Ports

Special pins Pins

‰ Single master IIC

Overview

Pin Description

Pin Configuration

Pin Specification

3 Pin Function Summary 1/6

Pin Functions

4 Pin Function Summary 2/6

5 Pin Function Summary 3/6

6 Pin Function Summary 4/6

7 Pin Function Summary 5/6

KEY1

8 Pin Function Summary 6/6

Block Diagram

Block Diagram

Electrical Characteristics

Absolute Maximum Ratings *2,*3 voltages referenced

To Vss

MIN TYP

1 Crystal Oscillator

MIN TYP MAX

Clock duty rate should be 45% to 55%

Twh2 Twl2 Twr2 Twf2 Twc2

Twh1 Twl1 Twr1 Twf1 Twc1

Characteristics

5 AC Zero-Cross Detector

VDD=3.3 V,V IN=V SS

Pin 7 P80 to P87 Input high voltage

LSB

Converter Characteristics *2

Resolution *1 Bits Reference voltage low level

General Usage

Precautions

1 Unused Pins only for input

Unused Pins

3 Unused I/O pins high impedance output at reset

Reset Input Voltage Reset pin low level Time

Power Supply

6 An Example for Emitter follower type Power Supply Circuit

Power Supply Circuit

Package Code LQFP064-P-1414

Package Dimension

Package Code TQFP064-P-1010C

Chapter CPU Basics

CPU Basics

1 Block Diagram and Function

CPU Control Registers

2 CPU Control Registers

Readable / Writable Part of bit is only readable

Instruction Execution Controller

2 Instruction Execution Controller Configuration

Registers for Address

Pipeline Process

Registers for Data

DW0

DW1

3 Processor Status WordPSW

Processor Status Word

3 Interrupt Mask Level and Interrupt Acceptance

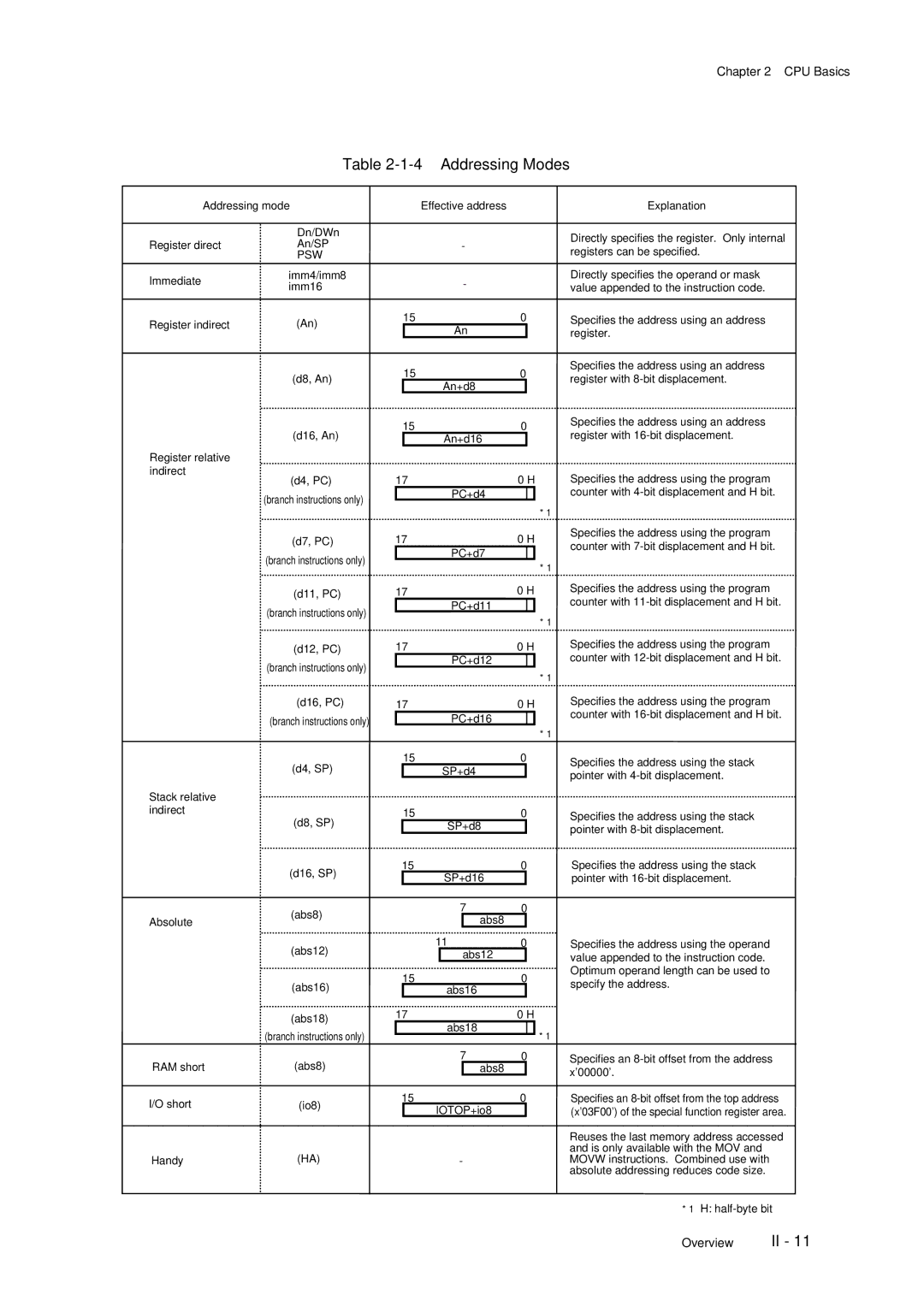

Addressing Modes

PSW

4 Addressing Modes

Memory Mode

1 Memory Mode Setup

Memory Space

2. Internal ROM / Internal RAM

Single-chip Mode

3 Register Map

Special Function Registers

Bus Controller

Bus Interface

2 Memory Control Register Memctr x03F01 R/W

Control Registers

3 Memory Area Control Register Areactr x03F03, R/W

„Memory Area Control Register Areactr

4 Bus Mode Control Register CSMDn x03F05 to x03F09, R/W

„Bus Mode Control Register CSMDn

1 Transition Between Operation Modes

Standby Function

II 20 Standby Functions

2 Operating Mode and Clock Oscillation Cpum x3F00, R/W

CPU Mode Control Register

Transition between Slow and Normal

Processing inside parentheses is handled by hardware

Transition to Standby Modes

NOP

Oscmd

Clock Switching

CPU

Bank area Address range DBA1 DBA0

Bank Setting

Bank Function

Address Range

„Bank Register for Source Address

Sbnkr

Dbnkr

Bank Memory Space

„Single Chip Mode

Correction Sequence

ROM Correction

ROM Correction

Rcctr

ROM Correction Control Register

„ROM Correction Address 1 Setting Register RC1AP

„ROM Correction Address 2 Setting Register RC2AP

Correspondence

RC2APH

12 Initial Routine for ROM Correction

ROM Correction Setup Example

RC0VL, RC0VH

RC0VL = xB4 RC0VH =

06BB FF

Corrected at second to the ROM correction address

RC1VL = xBC

RC1VH =

Reset operation

Reset

2 Reset Released Sequence

Wdctr

Oscillation Stabilization Wait time

Nrst Stop

Dlyctr

„Oscillation Stabilization Wait Time Control Register

Loop MOV

Setting of the Register Protection Function

Rewrite Procedure

Register Protection

Chapter Interrupts

III 2 Overview

Interrupt Functions

Functions

CPU core

PSW

RTI

Operation

2 Interrupt Vector Address and Interrupt Group

3 Interrupt Priority Outline

Generated interrupt level IL

Level judgement. Accepted if Ilim

Interrupts

PSW →

Contents of the PSW are saved to the stack

PC bits 16-9 → SP+2

PC bits 8-1 → SP+1

6 Processing Sequence for Maskable Interrupts

Maskable Interrupt

III 12 Overview

7 Processing Sequence with Multiple Interrupts Enabled

Interrupt Flag Setup

Interrupt request flag IR setup by the software

Interrupt flag setup procedure

Control Registers

Registers List

1 Interrupt Control Registers

1 Non-Maskable Interrupt Control Register NMICRx03FE1, R/W

Interrupt Control Registers

LV1

IRQ0ICR REDG0 IRQ0IE IRQ0IR

3 External Interrupt 1 Control Register IRQ1ICR x03FE3, R/W

IRQ2 LV1 LV0

IRQ2ICR REDG2 IRQ2IE IRQ2IR

IRQ3ICR REDG3 IRQ3IE IRQ3IR

5 External Interrupt 3 Control Register IRQ3ICR x03FE5, R/W

IRQ4ICR REDG4 IRQ4IE IRQ4IR

6 External Interrupt 4 Control Register IRQ4ICR x03FE6, R/W

TM0

TM0ICR TM0IE TM0IR LV1

TM1

TM1ICR TM1IE TM1IR LV1

TM4

TM4ICR TM4IE TM4IR LV1

TM5

TM5ICR TM5IE TM5IR

TM6

TM6ICR TM6IE TM6IR LV1

Tbicr Tbie Tbir LV1

15 Time Base Interrupt Control Register Tbicr x03FF0, R/W

TM7

TM7ICR TM7IE TM7IR LV1

T7OC2IE

T7OC2IR

SC0RIE SC0R SC0R LV1 LV0

SC0RIR

SC0TIE SC0T SC0T LV1 LV0

SC0TIR

SC1RIE SC1R SC1R LV1 LV0

SC1RIR

SC1TIE SC1T SC1T LV1 LV0

SC1TIR

SC3

SC3ICR SC3IE SC3IR LV1 LV0

SC4

SC4ICR SC4IE SC4IR LV1 LV0

Adicr Adie Adir

ATC1IR

ATC1IE

ATC1

1 External Interrupt Functions

External Interrupts

External Interrupts

P23/IRQ3 Noise filter3 Polarity Inversion Edge detection

3 External Interrupt 4 Interface Block Diagram

External Interrupt 4 Interface Block Diagram

Readable / Writable

2 External Interrupt Control Register

NFCTR0 P21IM

NF0EN

NF1EN

5 Noise Filter Control Register 1 NFCTR1 x03F8D, R/W

6 Both Edges Interrupt Control Register Edgdt x03F8F, R/W

7 Port 6 Key Interrupt Control Register P6IMD x03F3E, R/W

Port 6 Key Interrupt Control Register P6IMD

IRQ4IE

Programmable Active Edge Interrupt

REDG4

Rising edge as the active edge for interrupts

IRQ2IE

Both Edges Interrupt

Key Input Interrupt

External interrupt 4 source to the port 6 key

IRQ4SEL

Noise Filter

3 Noise Remove Function

4 Sampling Cycle / Time of Noise Remove Function

8 Noise Remove Function Operation

IRQ0IE

REDG0

Interrupt active edge to the rising edge

NF0EN

9 AC Line Waveform and IRQ1 Generation Timing

AC Zero-Cross Detector

IRQ1IE

Page

Chapter Ports

1 I/O Port Functions

1 I/O Port Diagram

1 I/O Port Status at Reset Single chip mode

Port Status at Reset

2 I/O Port Control Registers List 1/2

3 I/O Port Control Registers List 2/2

Description

Port

P0IN P0DIR

Registers

2 Block diagram P00

4 Block diagram P02

6 Block Diagram P04

8 Block Diagram P06

IV 12 Port

Port 1 input register P1IN x03F21, R

Port 1 output mode register P1OMD X03F2F, R/W

P10 Output Control register P1TCNT X03F7E, R/W

4 Block Diagram P10, P12, P14

Port 2 IV

Port 2 input registerP2IN x02F22, R

2 Block Diagram P20, P22 to P24

4 Block Diagram P27

Port 5 IV

Port 5 input register P5IN x03F25, R

2 Block Diagram P50

4 Block Diagram P52

6 Block Diagram P54

IV 26 Port

Port 6 output register P6OUT x03F16, R/W

Port 6 Synchronous Output Control Register P6SYOX03F1E, R/W

3 Block Diagram P60 to P67

IV 30 Port

Port 7 output register P7OUT x03F17, R/W

2 Port 7 Registers 2/2

Block Diagram P70

5 Block Diagram P72

7 Block Diagram P74

9 Block Diagram P76, P77

8Port

Port 8 output register P8OUT x03F18, R/W

Port 8 LED Control register P8LED x03F1D, R/W

3 Block Diagram P80 to P87

9Port a

Port a output register Paout X03F1A, R/W

Port a Input control register Paimd X03F3C, R/W

3 Block Diagram PA0 to PA1

Real Time Output Control Port

10-1 shows the real time output control register of port

10-1 Real Time Output Control Registers

IV 46 Real Time Output Control Port

10-1 Real Time Output Control Timing

Synchronous output Port

11-1 Synchronous Output Control Block Diagram

11-1 Synchronous Output Control Registers

11-1 shows the synchronous output control registers of port

11-2 Synchronous Output Event

11-2 Synchronous Output Timing by Event Generation IRQ2

IRQ2

Setup Example

Chapter Prescaler

Prescaler

1 Peripheral Functions Used with Prescaler Output

Peripheral Functions

Block Diagram

Control Register

1 shows registers to control prescaler

1 Prescaler Control Registers

1 Prescaler Control Register Pscmd x03F6F, R/W

„Timer 1 prescaler selection register CK1MD

2 Timer 0 Prescaler Selection Register CK0MD x03F56, R/W

„Timer 5 Prescaler Selection Register CK5MD

„Timer 4 Prescaler Selection Register CK4MD

„Serial Interface 1 Transfer Clock Selection Register SC1CKS

„Serial Interface 3 Transfer Clock Selection Register SC3CKS

CK4MD

Operation

CK0MD

CK1MD

TM0BAS

Pscen

Pscmd to

Chapter Bit Timers

TM0IRQ TM1IRQ TM4IRQ TM5IRQ

1 shows functions of each timer

1 Timer Functions

Functions

TM1MD

„Timers

„Timer

Block Diagram

Diagram

„Remote Control Carrier Output Block Diagram

MUX

Rmctr

1 8-bit Timer Control Registers

TM4BC

„Timer 5 Compare Register TM5OC

Programmable Timer Registers

„Timer 1 Compare Register TM1OC

„Timer 4 Compare Register TM4OC

„Timer 1 Binary Counter TM1BC

„Timer 4 Binary Counter TM4BC

„Timer 5 Binary Counter TM5BC

TM0PWM

Timer Mode Registers

TM0MD

TM0EN

TM1CAS

„Timer 1 Mode Register TM1MD

TM1MD

TM1EN

TM4MOD

„Timer 4 Mode Register TM4MD

TM4MD

TM4EN

TM5MOD

„Timer 5 Mode Register TM5MD

TM5MD

TM5EN

Rmbtms

„Remote Control Carrier Output Control Register Rmctr

1 Clock Source Timers 0, 1, 4 and 5 at Timer Operation

8-bit Timer Count

1 Count Timing of Timer Operation Timers 0, 1, 4

TM0EN

TM0PWM

TM0MOD

TM0IE

1 Event Count Input Clock

8-bit Event Count

2 Count Timing of Synchronous TMnIO Input Timers 0, 1, 4

TM0ICR

P1DIR1

VI 22 8-bit Event Count

8-bit Timer Pulse Output

1 Timer Pulse Output Pins

„Count Timing of Timer Pulse Output Timers 0, 1, 4

P1DIR0

P1OMD0

Bit Timers

1 Output Pins of PWM Output

„Count Timing of PWM Output at normal Timers 0, 4

8-bit PWM Output

2 Count Timing of PWM Output when compare register is

PWM operation

P1DIR x3F31 Control register P1DIR to 1 for the output Bp0

TM0EN

8-bit Timer Synchronous Output

1 Synchronous Output Port Timer 1, Timer

„Count Timing of Synchronous Output Timer 1, Timer

Pscmd x3F6F Prescaler counting Bp0

TM1EN

TM1CAS

TM1BAS

VI 32 Synchronous Output

1 Timer for Serial Interface Transfer Clock

„Timing of Serial Interface Transfer Clock Timers 4

Serial Interface Transfer Clock Output

TM4BAS

TM4EN

TM4PWM

TM4MOD

Bit Timers

Simple Pulse Width Measurement

1 Simple Pulse Width Measurement Able Pins Timers 0, 4

REDG2

IRQ2ICR

VI 38 Simple Pulse Width Measurement

Cascade Connection

10-1 Timer Functions at Cascade Connection

VI 40 Cascade Connection

Timer 1 mode register to 0 to stop timer 0

TM1MD x3F55 Timer 1 counting Bp3

Connection

TM1IE

11-1 Duty Cycle of Remote Control Carrier Output Signal

Remote Control Carrier Output

TM0RM

Rmoen

Rmbtms

RMDTY0

Normal timer operation

Page

Chapter Bit Timer

1 16-bit Timer Functions

1 shows the functions of timer

„Timer 7 Block Diagram

1 Timer 7 Block Diagram

1 shows the registers that control timer

1 16-bit Timer Control Registers

Readable/Writable Readable only

„Timer 7 Compare Register 2 TM7OC2

1 Timer 7 Compare Register 1 Lower 8 bits TM7OC1L x03F72, R

„Timer 7 Preset Register 2 TM7PR2

5 Timer 7 Preset Register 1 Lower 8 bits TM7PR1L x03F74, R/W

9 Timer 7 Binary Counter Lower 8 bits TM7BCL x03F70, R

TM7CK0

TM7EN

TM7CL

„Timer 7 Mode Register 2 TM7MD2

16-bit Timer Count

2 shows the clock source that can be selected

2 Clock Source at Timer OperationTimer

VII 12 16-bit Timer Count

TM7IE

TM7EN

TM7BCR

Compare match as a binary counter clear

VII 14 16-bit Timer Count

16-bit Event Count

1 Count Timing TM7IO Input Timer

2 Count Timing of Synchronous TM7IO Input Timer

Counter

Compare match as a clear source of binary

VII 18 16-bit Event Count

1 Timer Pulse Output Pin

16-bit Timer Pulse Output

1 Count Timing of Timer Pulse Output Timer

„Count Timing of Timer Pulse Output Timer

TM7PWM

Pulse output

Source of a binary counter

TM7CL

„Count Timing of Standard PWM Output at NormalTimer

16-bit Standard PWM Output

1 PWM Output Pin

PWM output shows H , when TM7EN flag is stopped at

4 Output Waveform of TM7IO Output Pin

VII 26 16-bit Standard PWM Output

Cycle/Duty can be changed consecutively

16-bit High Precision PWM Output

VII 28 16-bit High Precision PWM Output

Also, set the T7PWMSL flag to 1 to select

P1OMD4

VII 30 16-bit High Precision PWM Output

1 Count Timing of Synchronous Output Timer

16-bit Timer Synchronous Output

Source of the binary counter

TM7EN

Capture Trigger

16-bit Timer Capture

3-4. Programmable active Edge Interrupt

VII 36 16-bit Timer Capture

3 Pulse Width Measurement of External Interrupt

External interrupt IRQ 0 input Pulse width to be measured

T7ICEN

T7ICEDG

Chapter Time Base Timer Bit Free-running Timer

Tbirq TM6IRQ

1 Clock Source and Generation Cycle

1 Block Diagram Timer 6, Time Base Timer

„Timer 6, Time Base Timer Block Diagram

Control Registers

1 shows the registers that control timer 6, time base timer

Tbclr

„Timer 6 Compare Register TM6OC

TM6BC

TM6OC

TM6MD

TM6CKS0

TM6CLRS

1 Clock Source at Timer Operation Timer

8-bit Free-running Timer

2 1 minute-timer, 1 second-timer Setup Timer

TM6BC

Bp1 Hz1 s

2 Count Timing of Timer Operation Timer

Above steps 1, 2 can be set at once

TM6ICR x3FEF Bp1

TM6IE

Set the TM6IE flag of the TM6ICR register to

Viii

1 Time Base Timer Interrupt Generation Cycle

Time Base Timer

1 Count Timing of Timer Operation Time Base Timer

Tbicr

If the interrupt request flag had already been

Tbie

Chapter Watchdog Timer

1 Block Diagram Watchdog Timer

„Watchdog Timer Block Diagram

1 Watchdog Timer Control Register Wdctr x03F02, R/W

Watchdog timer cannot stop, once it starts operation

2 The Lowest Value for Watchdog Timer Clear

1 Watchdog Timer Period

IX 6 Operation

Setup Example

Manage the suitable execution

On the interrupt service routine,

Tbnz Nmicr WDIR, Wdpro

Maskable interrupt control register Nmicr is

Buzzer

1 Block Diagram Buzzer

„Buzzer Block Diagram

„Oscillation Stabilization Wait Timer Control Register

BUZS2 BUZS1 BUZS0

1 Buzzer Output Frequency

Operation X

Page

Serial Interface 0,1

P01/SBI1A/RXD1A P74/SBI1B/RXD1B P02/SBT1A P75/SBT1B

1 Serial Interface 0, 1 used pins

1 Serial Interface 0, 1 Functions

1 shows functions of serial interface 0

„Serial Interface 0 Block Diagram

1 Serial Interface 0 Block Diagram

„Serial Interface 1 Block Diagram

2 Serial Interface 1 Block Diagram

1 shows registers to control serial interface 0

1 Serial Interface 0, 1 Control Registers

Readable / Writable Readable only

„Serial Interface 0 Transmissin Data Buffer TXBUF0

Serial Interface 0 Data Buffer Registers

„Serial Interface 0 Mode Register 0 SC0MD0

Serial Interface 0 Mode Registers

4 Serial Interface 0 Mode Register 1 SC0MD1 x03F93, R/W

„Serial Interface 0 Mode Register 1 SC0MD1

SC0BRKF flag is only for reading

„Serial Interface 0 Mode Register 2 SC0MD2

All flags are only for reading

„Serial Interface 0 Mode Register 3 SC0MD3

„Serial Interface 0 Port Control Register SC0ODC

„Serial Interface 0 Transfer Clock Selection Register SC0CKS

„Serial Interface 1 Transmissin Data Buffer TXBUF1

Serial Interface 1 Data Buffer Registers

„Serial Interface1 Mode Register 0 SC1MD0

Serial Interface 1 Mode Registers

12 Serial Interface 1 Mode Register 1 SC1MD1 x03F9B, R/W

„Serial Interface 1 Mode Register 1 SC1MD1

SC1BRKF flag is only for reading

„Serial Interface 1 Mode Register 2 SC1MD2

14 Serial Interface 1 Mode Register 3 SC1MD3 x03F9D, R

„Serial Interface 1 Mode Register 3 SC1MD3

„Serial Interface 1 Port Control Register SC1ODC

SC1CKS

„Serial Interface1 Transfer Clock Selection Register SC1CKS

1 Synchronous Serial Interface Activation Factor

Clock Synchronous Serial Interface

XI 22 Operation

TXBUFn

2 Transmission Data Output Edge and Received Data Input Edge

3 Synchronous Serial Interface Internal Clock Source

XI 26 Operation

5 Other Control Flag

4 Last Bit Data Length of Transfer Data

„Trasnmission Timing

Tmax=1.5 T Tmax=2 T

„Reception Timing

9 Reception Timing rising edge, start condition is enabled

11 Reception Timing falling edge, start condition is enabled

XI 32 Operation

Serial interface 0 Synchronous Serial Interface Pin Setup

XI 34 Operation

P7DIR P7DIR0 P7DIR P7DIR7

Serial interface 1 Synchronous Serial Interface Pin Setup

SC0ODC SC1SEL

XI 38 Operation

MSB

XI 40 Operation

Interrupt Flag Setup

17 Uart Serial Interface Functions

Uart Serial Interface

Serial Interface 0

18 Uart Serial Interface Transmission / Reception Data

15 shows the data format at Uart communication

20 Parity Bit of Uart Serial Interface

19 Uart Serial Interface Frame Mode

21 Reception Error Source of Uart Serial Interface

Serial Interface 0

XI 48 Operation

„Transmission Timing

16 Transmission Timing parity bit is enabled

18 Reception Timing parity bit is enabled

23 Uart Serial Interface Transfer Rate Setup Register

22 Uart Serial Interface Transfer Rate Setup Register

24-1 Uart Serial Interface Transfer Rate decimal

24-2 Uart Serial Interface Transfer Rate decimal

9600 19200 28800 31250 38400 MHz Timer

SC0ODC SC0SEL

Serial interface 0 Uart Serial Interface Pin Setup

27 Uart Serial Interface 0 Pin Setup 1 channel, at reception

SC1ODC SC1SEL

Serial interface 1 Uart Serial Interface Pin Setup

31 Uart Serial Interface 1 Pin Setup 1 channel, at reception

33 Uart Interface Transmision Reception Setup

Serial Interface 0

XI 60 Operation

Serial Interface

1 Serial Interface 3 Functions List

1 shows the functions of serial interface

12-1-2 Block Diagram

1 Serial Interface 3 Control Registers

1 shows the registers to control serial interface

SC3TRB

Data Register

„Serial Interface 3 Mode Register 0 SC3MD0

Mode Registers

3 Serial Interface 3 Mode Register 1 SC3MD1 x03FA9, R/W

„Serial Interface 3 Mode Register 1 SC3MD1

„Serial Interface 3 Control Register SC3CTR

„Serial Interface 3 Port Control Register SC3ODC

1 Activation factor of Synchronous Serial Interface

„Receive Bit Count and First Transfer Bit

1-1 Transfer Bit Count and First Transfer Bit at MSB first

2 Synchronous Serial Interface Internal Clock Source

4 Last Bit Data Length of Transmission Data

3 Input Edge/Output Edge of Transmission/Received Data

2 Transmission Timing Falling edge, Enable Start Condition

4 Transmission Timing Rising edge, Enable Start Condition

6 Reception Timing Rising edge, Enable Start Condition

8 Reception Timing Falling edge, Enable Start Condition

XII 18 Operation

SBI3/SBO3

XII 20 Operation

P5PLUP5PLU1 P5PLUP5PLU2

SC3ODCSC3ODC0 SC3ODCSC3ODC1

XII 22 Operation

Function Port Serial data input Serial clock I/O

XII 24 Operation

Interrupt Flag Setup

XII 26 Operation

11 IIC Serial Interface Functions

Single Master IIC Interface

12 Start Condition and Stop Condition

13 ACK Bit Reception Timing after Transmission of 8-Bit Data

12 IIC Interface Clock Source

Addressing format master transmission

Addressing format master reception

Free data format master transmission

16 Master Transmission Timing, -3-17 Master Reception Timing

16 Master Transmission Timing

„Master Transmission Timing

17 Master Reception Timing

„Master Reception Timing

13 Pin Setup 2 channels, at transmission

14 Pin Setup 2 channels, at reception

15 Conditions Single Master IIC Communication Setup

Serial Interface

XII 38 Operation

Is . When SC3ACKO = 1, the reception at

XII 40 Operation

Serial Interface

1 Serial interface 4 Functions List

SC4STR

„Serial interface 4 Block Diagram

1 Serial interface 4 Control Registers

„Serial interface 4 Transmission Data Buffer SC4TXB

1 Serial interface 4 Reception Data Buffer SC4RXB x03FAD, R

„Serial interface 4 Addressing Register 0 SC4AD0

„Serial interface 4 Addressing Register 1 SC4AD1

I2CAD7 I2CAD6 I2CAD5 I2CAD4 I2CAD3 I2CAD2 I2CAD1 I2CAD0

5 Serial interface 4 Status Register SC4STR x03FAC, R

„Serial interface 4 Status Register SC4STR

„Serial interface 4 Port Control Register 1 SC4ODC1

„Serial interface 4 Port Control Register 0 SC4ODC0

Operation Xiii

Pin Setup

SC4ODC0

SC4ODC1

Setup Example of the Slave IIC Serial Interface

Xiii 12 Operation

Automatic Transfer Controller

14-1-1 ATC1

1 ATC1 Trigger Factors

„ATC Transfer Modes

Transfer Modes

1 ATC1 Block Diagram

„ATC1 Block Diagram

1 ATC1 Control Registers

1 shows the registers used to control ATC1

1 ATC1 Control Register 0 AT1CNT0 x03FD0, R/W

„ATC1 Control Register 0 AT1CNT0

„ATC1 Transfer Counter AT1TRC

„ATC1 Control Register 1 AT1CNT1

„ATC1 Memory Pointer 1 AT1MAP1

„ATC1 Memory Pointer 0 AT1MAP0

Basic Operations and Timing

„Transfer end

„Data transfer

„Memory pointer 1 functions

Setting the Memory Address

„Setting the transfer addresses to the memory pointers

„Memory pointer 0 functions

Setting the Data Transfer Count

„Transfer data counter AT1TRC function

„The transfer data counter AT1TRC

Setting the Data Transfer Modes

„Data transfer modes

„Standard and burst transfers

Transfer Mode

AT1MAP0

AT1MAP1

3 Transfer Mode

4 Transfer Mode

5 Transfer Mode

6 Transfer Mode

7 Transfer Mode

8 Transfer Mode

Automatic Transfer Controller

9 Transfer Mode

Automatic Transfer Controller

10 Transfer Mode

Automatic Transfer Controller

11 Transfer Mode

Automatic Transfer Controller

12 Transfer Mode a

Transfer mode a

13 Transfer Mode B

Transfer Mode B

14 Transfer Mode C

Transfer Mode C

15 Transfer Mode D

Transfer Mode D

16 Transfer Mode E

Transfer Mode E

17 Transfer Mode F

Transfer Mode F

AT1EN

Setup Example

Fmode

AT1ACT

Setup Example

Page

Converter

1 A/D Converter Functions

1 shows the A/D converter functions

Hold

1 A/D Converter Control Registers

1 shows the registers used to control A/D converter

„A/D Converter Control Register 0 ANCTR0

ANCTR0 ANSH1

Anlade

Anstsel

„A/D Converter Control Register 1 ANCTR1

„A/D Converter Control Register 2 ANCTR2

ANCTR2 Anst

ANBUF1

Data Buffers

XV 8 Operation

1 Operation of A/D Conversion

3 Sampling Time of A/D Conversion and A/D Conversion Time

Setup

1 Input Pins of A/D Converter Setup

2 A/D Conversion Clock and A/D Conversion Cycle

4 A/D Ladder Resistor Control

5 A/D Conversion Activation Factor Selection

6 A/D Conversion Starting

4 Interrupt Flag Setting

Converter

Padir

Converter

2 A/D Converter Recommended Example

Recommended Connection with A/D Converter

Page

Converter

1 D/A Converter Functions

1 shows the D/A converter functions

Operation XVI

Readable/Writable

1 D/A Converter Control Registers

1 D/A Converter Control Register Dactr x03FBE R/W

Control Register Dactr

2 D/A Converter Input Data Register 01 DADR01 x03FBF R/W

Input Data Registers

Paplud

Page

Appendices

OFF OP0 OP1 OP2 OP3 OP4 OP5

Probe Switches

PRB-MBB101C77-M

Top view of MBB board

MBB board PRB-MBB101∗∗∗-M

PX-CN101-M

MBB board PRB-MBB101∗∗∗-M

PRB-ADP101-64-M

MBB board PRB-MBB101C77-M

17-1-4PRB-DMY101C77-M

17-2 Special Function Registers List

Special Function Registers List

Xvii 8 Special Function Registers List

TM1OC2

Xvii 10 Special Function Registers List

SC0ODC

Xvii 12 Special Function Registers List

Nmicr

Xvii 14 Special Function Registers List

I2CAD7 I2CAD6 I2CAD5 I2CAD4 I2CAD3 I2CAD2 I2CAD1 I2CAD0

MOV

Instruction Set

Instruction Set

D4 sign-extension D7 sign-extension D11 sign-extension

Cbeq

JMP

INC ADD DEC Addw INC2 DEC2 CLR SUB

Instruction Map

17-4

Ver2.12001.03.26

Page

Flash Eeprom

XVIII-2 Overview

Eeprom

1 Memory Map in Internal Flash Eeprom

1 Differences between Mask ROM version and Eprom version

Differences between Mask ROM version and Eprom version

Pin Descriptions

1 Pin Configuration LQFP064-P-1414

Sens

Absolute Maximum Ratings*2,*3

Operating Conditions

Normal mode fs=fosc/2, Slow mode fs=fx/2

DC Characteristics

1 Reprogramming Flow of Internal Flash Eeprom

Reprogramming Flow

Prom writer mode

2 Pin Configuration for Socket Adaptor

„Pin Configuration for Socket Adaptor

Onboard Serial Programming Mode

1 Target Board for programming using the YDC Serial Writer

X06088 to X23FFF This area stores the user program

This section describes each memory space of Flash Eeprom

XVIII-15

3 Target Board for programming using the PanaX Serial Writer

Maximum output current of pin I OL

Pull-up resistor value

Pull-up resistor RupMin X Load capacity

MN101C77C/F77G

Sales Offices