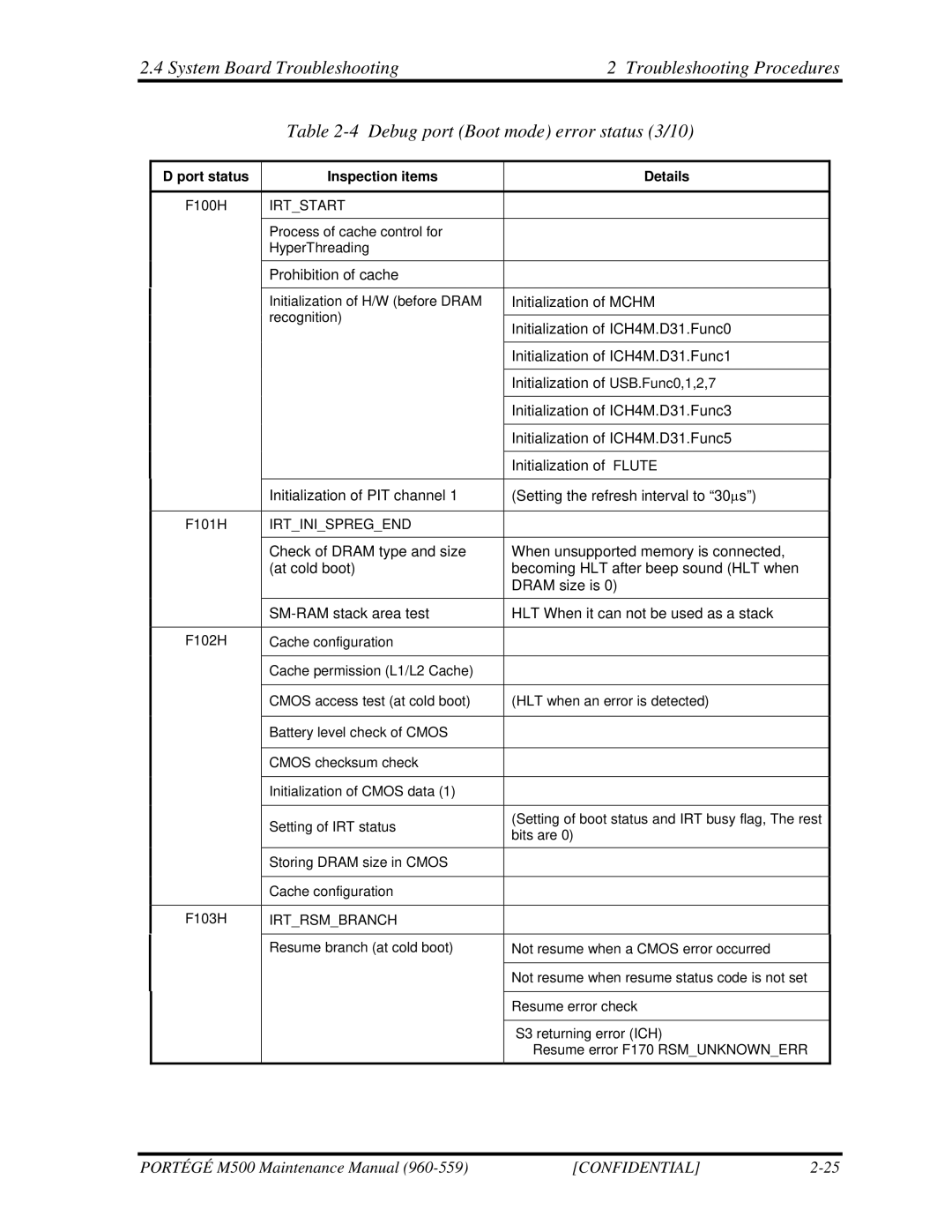

2.4 System Board Troubleshooting | 2 Troubleshooting Procedures |

Table

D port status | Inspection items | Details |

|

|

|

F100H | IRT_START |

|

|

|

|

| Process of cache control for |

|

| HyperThreading |

|

|

|

|

| Prohibition of cache |

|

| Initialization of H/W (before DRAM | Initialization of MCHM |

| recognition) |

|

| Initialization of ICH4M.D31.Func0 | |

|

| |

|

|

|

|

| Initialization of ICH4M.D31.Func1 |

|

|

|

|

| Initialization of USB.Func0,1,2,7 |

|

|

|

|

| Initialization of ICH4M.D31.Func3 |

|

|

|

|

| Initialization of ICH4M.D31.Func5 |

|

|

|

|

| Initialization of FLUTE |

|

|

|

| Initialization of PIT channel 1 | (Setting the refresh interval to “30μs”) |

|

|

|

F101H | IRT_INI_SPREG_END |

|

|

|

|

| Check of DRAM type and size | When unsupported memory is connected, |

| (at cold boot) | becoming HLT after beep sound (HLT when |

|

| DRAM size is 0) |

|

|

|

| HLT When it can not be used as a stack | |

|

|

|

F102H | Cache configuration |

|

|

|

|

| Cache permission (L1/L2 Cache) |

|

|

|

|

| CMOS access test (at cold boot) | (HLT when an error is detected) |

|

|

|

| Battery level check of CMOS |

|

|

|

|

| CMOS checksum check |

|

|

|

|

| Initialization of CMOS data (1) |

|

|

|

|

| Setting of IRT status | (Setting of boot status and IRT busy flag, The rest |

| bits are 0) | |

|

| |

|

|

|

| Storing DRAM size in CMOS |

|

|

|

|

| Cache configuration |

|

|

|

|

F103H | IRT_RSM_BRANCH |

|

| Resume branch (at cold boot) | Not resume when a CMOS error occurred |

|

|

|

|

| Not resume when resume status code is not set |

|

|

|

|

| Resume error check |

|

|

|

|

| S3 returning error (ICH) |

|

| Resume error F170 RSM_UNKNOWN_ERR |

|

|

|

PORTÉGÉ M500 Maintenance Manual | [CONFIDENTIAL] |