Software Trigger Register

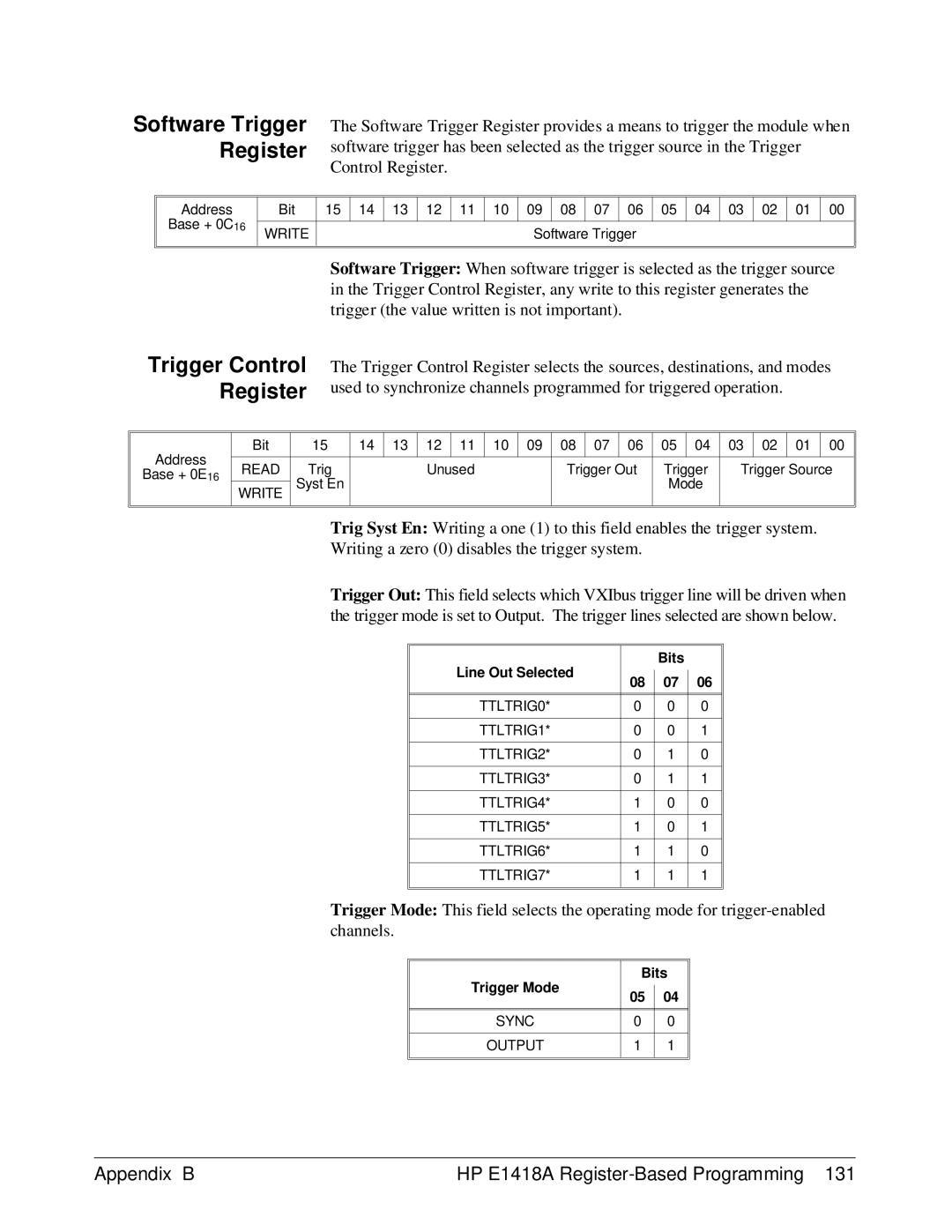

The Software Trigger Register provides a means to trigger the module when software trigger has been selected as the trigger source in the Trigger Control Register.

Address

Base + 0C16

Bit | 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

WRITE |

|

|

|

|

|

| Software Trigger |

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Software Trigger: When software trigger is selected as the trigger source in the Trigger Control Register, any write to this register generates the trigger (the value written is not important).

Trigger Control Register

The Trigger Control Register selects the sources, destinations, and modes used to synchronize channels programmed for triggered operation.

Address | Bit | 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

READ | Trig |

|

| Unused |

|

| Trigger Out | Trigger | Trigger Source | ||||||||

Base + 0E16 |

|

|

|

| |||||||||||||

| Syst En |

|

|

|

|

|

|

|

|

| Mode |

|

|

|

| ||

| WRITE |

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Trig Syst En: Writing a one (1) to this field enables the trigger system.

Writing a zero (0) disables the trigger system.

Trigger Out: This field selects which VXIbus trigger line will be driven when the trigger mode is set to Output. The trigger lines selected are shown below.

Line Out Selected |

|

| Bits |

|

|

08 |

| 07 |

| 06 | |

|

| ||||

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

TTLTRIG0* | 0 |

| 0 |

| 0 |

|

|

|

|

|

|

TTLTRIG1* | 0 |

| 0 |

| 1 |

|

|

|

|

|

|

TTLTRIG2* | 0 |

| 1 |

| 0 |

|

|

|

|

|

|

TTLTRIG3* | 0 |

| 1 |

| 1 |

|

|

|

|

|

|

TTLTRIG4* | 1 |

| 0 |

| 0 |

|

|

|

|

|

|

TTLTRIG5* | 1 |

| 0 |

| 1 |

|

|

|

|

|

|

TTLTRIG6* | 1 |

| 1 |

| 0 |

|

|

|

|

|

|

TTLTRIG7* | 1 |

| 1 |

| 1 |

|

|

|

|

|

|

|

|

|

|

|

|

Trigger Mode: This field selects the operating mode for

Trigger Mode | Bits | ||

05 |

| 04 | |

| |||

|

| ||

|

|

|

|

|

|

|

|

SYNC | 0 |

| 0 |

|

|

|

|

OUTPUT | 1 |

| 1 |

|

|

|

|

|

|

|

|

Appendix B | HP E1418A |