STATus

STATus:QUEStionable:CONDition?

STATus:QUEStionable:CONDition? returns the value of the Questionable Status Condition Register. Reading the register does not affect its contents. Since only two bits are used in the HP E1418A and both those bits are defined to be events, this command always returns 0 and is included for compatibility purposes.

Parameters Returns:

Comments ∙ Bit 8 of this register (decimal 256) indicates the calibration condition. Bit 9 of this register (decimal 512) indicates the

∙*RST Condition: clears all conditions.

∙*CLS and STATus:PRESet do not affect bits in the Questionable Status Condition Register.

STATus:QUEStionable:ENABle

STATus:QUEStionable:ENABle <mask> specifies which bits of the Questionable Event Register are OR’d together to create the Questionable Data bit (bit 3) in the Status Byte Summary Register.

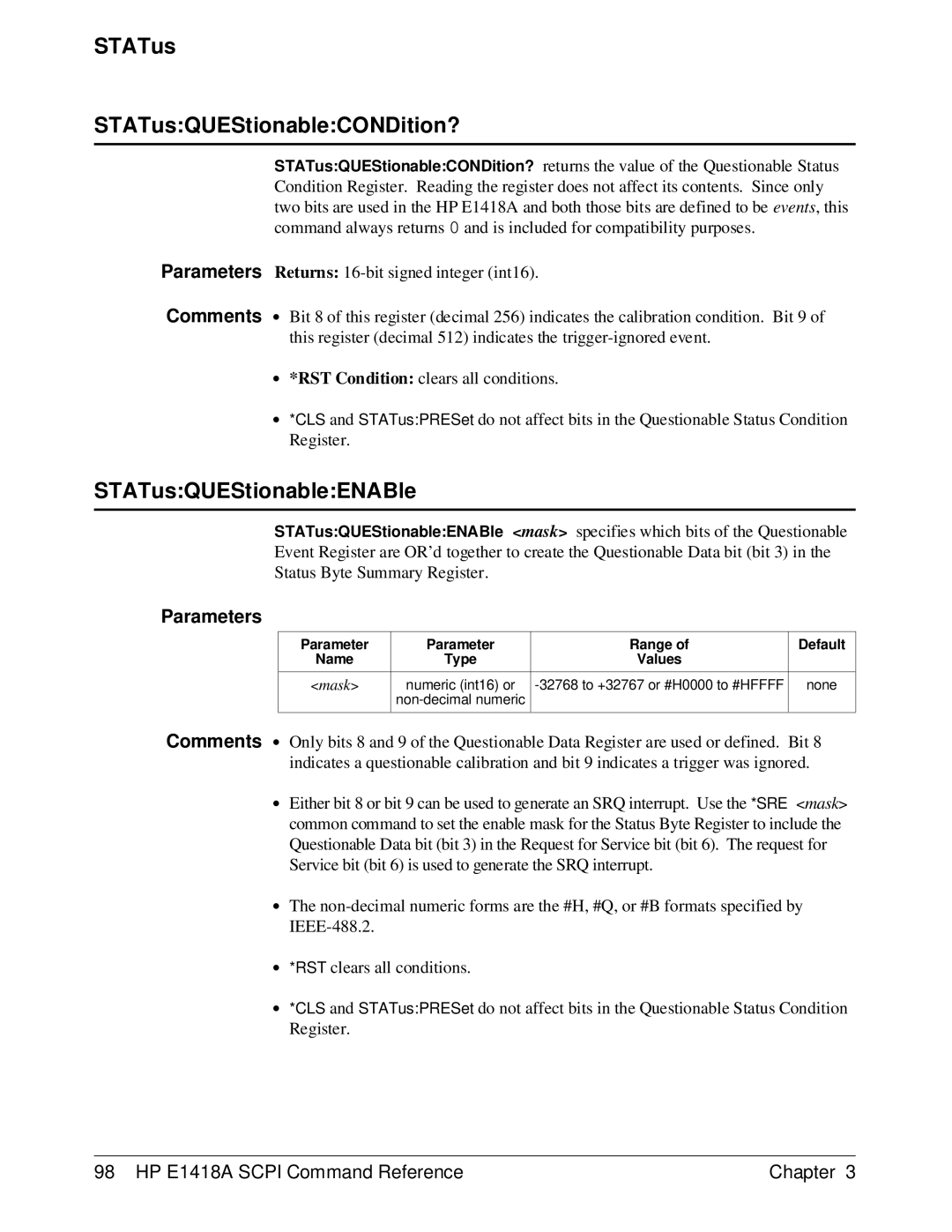

Parameters

Parameter | Parameter | Range of | Default |

Name | Type | Values |

|

|

|

|

|

<mask> | numeric (int16) or | none | |

|

|

| |

|

|

|

|

Comments ∙ Only bits 8 and 9 of the Questionable Data Register are used or defined. Bit 8 indicates a questionable calibration and bit 9 indicates a trigger was ignored.

∙Either bit 8 or bit 9 can be used to generate an SRQ interrupt. Use the *SRE <mask> common command to set the enable mask for the Status Byte Register to include the Questionable Data bit (bit 3) in the Request for Service bit (bit 6). The request for Service bit (bit 6) is used to generate the SRQ interrupt.

∙The

∙*RST clears all conditions.

∙*CLS and STATus:PRESet do not affect bits in the Questionable Status Condition Register.

98 HP E1418A SCPI Command Reference | Chapter 3 |