Issue

NDA-24300

Stock #

October

Liability Disclaimer

NEAX2400 IPX

Issue No 100 101 102 103 104 105 106 107 108 109

Issue No

251

Revision Sheet 5/9

403

479

555

Revision Sheet 9/9

System Operations and Maintenance Manual

Table of Contents

Table of Contents

116

LPM Accommodating UNIT/CIRCUIT Card Replacement Procedure

Table of Contents

Fault Repair Procedures

NDA-24300TABLE of Contents

Hard Time Clock Fault

Routine Maintenance Procedure

Chapter Maintenance Commands

DTF101N

List of Figures

301

List of Figures

List of Figures

NDA-24300LIST of Figures Page xiii Issue

List of Tables

List of Tables

NDA-24300LIST of Tables Page xv Issue

This page is for your notes

HOW to Follow this Manual

General

NDA-24300CHAPTER

When replacing a unit/circuit card with a spare

When performing routine maintenance

Introduction

Chapter

Administrative Management Procedures

Purpose

Summary of This Manual’s Contents

Basic Knowledge

System Configuration

System Configuration

3shows the face layout of IMG0

IMG0

4shows the face layout of IMG1

IMG1

5shows the face layout of IMG 2/3

Line Equipment Numbers Lens

Module Group

Unit

U2 U3 MG06 U0 U1

Group

Group Number Allocations

Level

Total of eight Levels Lv0 Lv7 can be assigned on each Group

Local Partition LP Number

11 LP Number Allocations

System Messages

System Message 3-E SUP Lock UP Failure Temporary NEC Tokyo

Fault Detecting Function

IOC CPU EMA

14 Fault Detection Block Diagram

System Maintenance Outline

Range of Faults Specification

15 General System Block Diagram

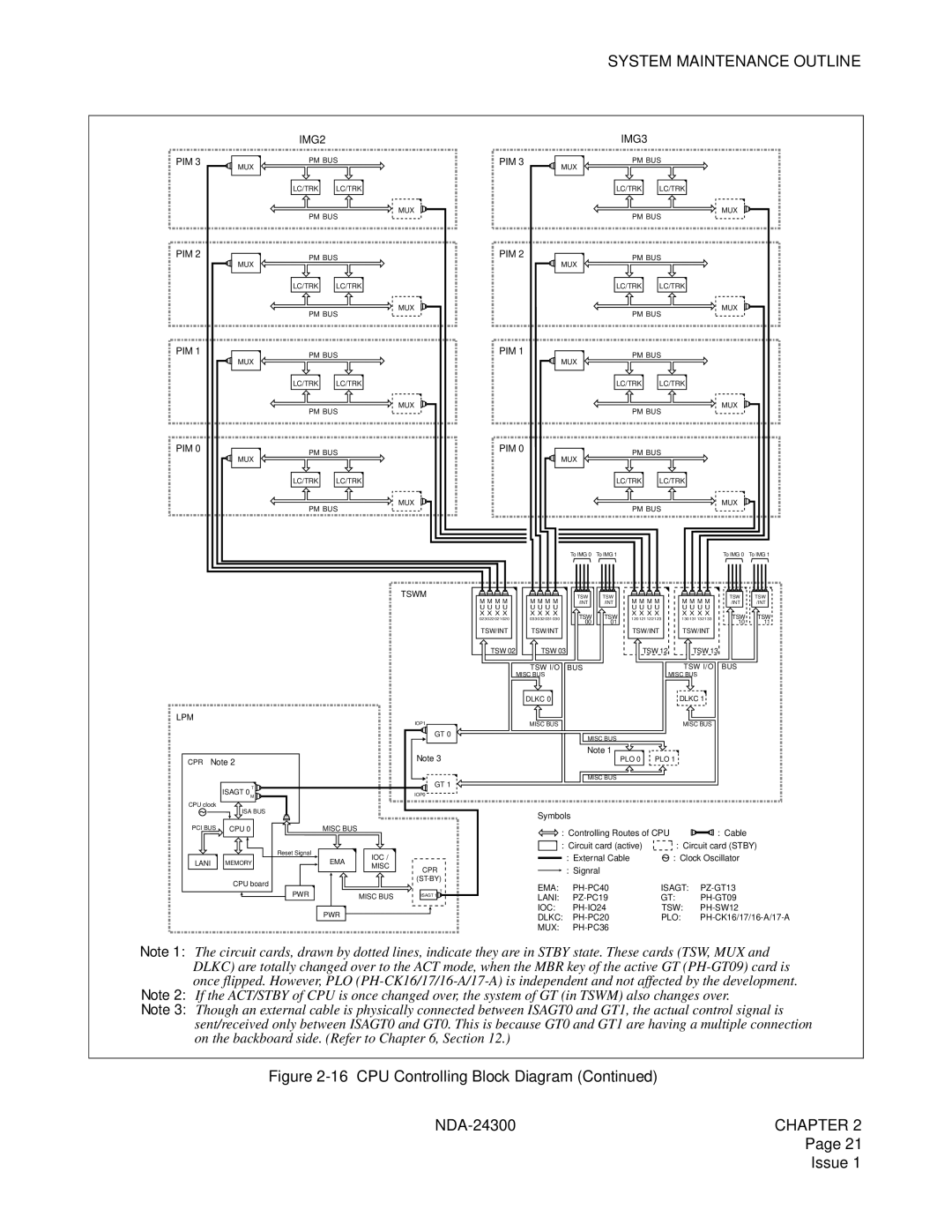

16 CPU Controlling Block Diagram

IMG2

17 Speech Path Block Diagram

IMG2 PIM

18 Speech Path Range of Fault

Explanation of Terms

Precaution about Diagnostic Procedure/Fault Repair Procedure

Sense 0~F Kind of Restart Remarks

19 3M Model 8012 Portable Field Service Kit

21 How to Set the ROM in IC Socket

22 How to Clean the Connector Portion

How to Follow Diagnostic Procedure/Fault Repair Procedure

Start

END

System Maintenance Outline

Judgment of fault status

Reporting Fault to NEC

Fault Reporting Method

16LCBE

Forwarding Faulty Circuit Card Method

This page is for your notes

System Messages

System Messages

System Initialize

Message no System Message

Message no System Message

Reset Interrupt

➃ Data Load Result after restart

Processing

B15 B11

Reference See , .2, for the repair procedure

CPU Clock Down

➁ Male-CPU Restart Information FF

➂ Related Call Information

Level Infinite Loop

SUP

➃ System Controlling Port B

➅ CPU Changeover Factors

➆ System ALM

➇ Data Analyzed by NEC Engineers

After detection of a clock fault

Memory Failure

➀ Information on Self-CPU Restart

= CPU #0/CPU #1

B1-Level Infinite Loop Permanent

➂ B-level Infinite Loop

B1-Level Infinite Loop Temporary

➀ ➁ ➂

Mate CPU Failure

➀ Mate-CPU Restart Information

Abnormal Interrupt

➀ ➁ ➂ ➃

Both TSW Failure Permanent

TSW Failure Permanent

➀ TSW system in which a fault is

Both TSW Write Failure

Detected B7 b6

TSW Write Failure

➂ Data Analyzed by NEC Engineers

➀ TSW card in which a fault is

Both TSW Clock Failure

➁ Clock status of No TSW

TSW Clock Failure

Both PLO Failure

➀ ➁ ➂ ➃ ➄

DCS Input Route Route Of Input Clock

PLO Failure

➁ Valid Information bit for Scan Data

System Messages

➀ MG number of fault detection

Module Group Down Failure

➁ Kind of failure

TSW ACT Change Report

NON

➂~➅ Status of ACT side TSW card

➆~➉ Status of ST-BY side TSW card

➀ System status of faulty Dlkc card

➂ Details on Switching Network

Dlkc Data Transfer Failure Permanent

Dlkc Data Transfer Failure Temporary

PLO Restore

Connected With Primary Oscillator M-OSC External Clock

➀ Faulty Circuit Card Mounting

Level Infinite Loop Permanent

Location

Level Infinite Loop Temporary

➁ PM Restart Type

Lock-Up Failure Permanent

➀ Faulty Circuit Card Location

Lock-Up Failure Temporary

Busy state and stops supplying power

➀ Location of faulty PM

48V Over Current

➀ Location of faulty circuit card

➁ Location of faulty circuit card

Ground Failure

➀ Location of PM Lens with a fault

➁ Kind of fault

➂ Time Slot No. of fault This data is

Valid only when the kind of fault is 08H

Digital Line Failure

➂ ➃ ➂ ➃

Digital Line Restore

This message displays when a digital line fault is restored

➀ Location of faulty line

➀ Unit and MG number of fault

Both TSW Ready Failure

Detection

Detection Reference See , .4, for the repair procedure

TSW Ready Failure

➀ Details on faulty Dlkc card

Dlkc Ready Failure

➀ Unit and MG number for MUX card with ready fault

➁ MG and system number for faulty MUX card

Reference See , .3 and .4, for the repair procedure

MUX Ready Failure

➀ Unit and MG number for MUX card with the ready fault

Both MUX Ready Failure

PCI Card Failure

➄ Error status on PCI slot

PCI Card Failure Recovered

➀ Detection of PCI restoration

➄ Details on error restoration PCI

Slot

Reference See , , for the repair procedure

System Failure

➀ Probable cause for failure

NON Fixed NON

RGU & Howler Failure

Line Load Control Start

Line Load Control Stop

When type of connection is Station connection

Bad Call Notification

➁ ➃ Station number see table b7 b6 b5 b4 b3 b2 b1 b0

➄ The called station number

When type of connection is Trunk connection

➄ Remote Route No

➅ Remote Route No

➆ Called Trunk No

➇ Not used ➈ Time Slot Number of Link ➉ Not used

When type of connection is ACD Trunk connection

B4-b7

System Messages

STA-Test Connection Data

➀ Test Item b0-b3 is valid only for Outgoing trunk test

Error Numbers and Their Meanings

Error no Meaning

➇ Tested Route No

= SST, WT = SDT = TRG = Sdtt

Emergency Call

➀ ➁ ➂ ➃ ➄ ➅➆ ➇ ➈ ➉ 11

Emergency Control Start

➀ Route Selection Time Pattern No

Assigned at Attendant Desk Console

Emergency Control Stop

➀ Suspension of Emergency Control

When calling party is Station

Abnormal Call Duration Data

➀ Calling party information

Calling station No. See table

When calling party is ATTCON/DESKCON

When calling party is Trunk

Route No. and Trunk No. See table

➃ Called party information

➄ Called Party Information

Station to Station Call

Type of called party 00 = Station 01 = Attendant Console

OG Call to outside IC Call from outside

Smdr Output Buffer Overflow Alarm

➀ Detail Information B7 b6 b5 b4 b3 b2 b1 b0

FS = 0, FE = 0/1

FS = 1, FE =

➂ Overflow Rate

➃ Overflow Rate

FS = 2, FE =

➁ Smdr Group No

➂ Port No

FS = 3, FE =

Smdr Output Buffer Overflow Release

➀ Detail Information

System Initialize With Data Load

➁ Load Status

System Messages

System Initialize

CPU MBR Key Turn on

CPU MBR Key Turn OFF

TSW MBR Key Turn on

➀ System status of TSW card

TSW MBR Key Turn OFF

TSW PLO Key Turn on

Operation

TSW PLO Key Turn OFF

Almc MB Key Turn on

➀ Frame No. and its kind

Almc MB Key Turn OFF

➀ Location of faulty Line/Trunk card b7 b6 b5 b4 b3 b2 b1 b0

PM MB Key Turn on

PM MB Key Turn OFF

➁ Location of faulty PFT card

NCU MB Key Turn on

NCU MB Key Turn OFF

Cyclic Diagnosis Normal

➀ Performed Diagnosis Item

00H Routine Diagnosis Start

➀ Performed Diagnosis Item

➁ Pending Diagnosis Menu SYS1

Index

10H Program Memory Verification Normal End

➀ Routine Diagnosis

➁ Information on HD

➂ Verification of Drive Number

20H Data Memory Verification Normal End

➁ Verification of HD

➂ Verification of Data Memory

30H TSW ACT/STBY Changeover Normal End

➁ Active TSW system after

Changeover

40H CPU ACT/STBY Changeover Normal End

50H No Trunk Ineffective Hold

➁ MG and Unit of No. of Trunk

Ineffective Hold

70H Call Forwarding Memory Clear Normal End

➁ Information on Periodic Backup

➂ Backup Data to No system

➃ Backup Data to No system

A0H Periodic Back-up Normal

C0H Detection of Remaining Link Normal End

Cyclic Diagnosis Information Error Detected

➀ Detected Error Item B7 b6 b5 b4 b3 b2 b1 b0

For Release 4 or later

10H Program Memory Verification Discrepancy

Diagnosis ➁ Verification of HFD number

➃ Data analyzed by NEC Engineers

11H Program Memory Verification Impossible HFD Fault

➀ Error detection by Routine

➃ Data analyzed by NEC Engineers ➄ Error Drive

Diagnosis ➁ Verification Impossible of HD

12H Program Memory Verification Impossible Fault at CPU side

20H Data Memory Verification Discrepancy

Diagnosis ➁ Verification of HFC

21H Data Memory Verification Impossible HFC Fault

➃ Error Type B7 b6 b5 b4 b3 b2 b1 b0

Diagnosis ➁ HFC Impossible Verification

➄ Single Code

➅ Data analyzed by NEC Engineers ➆ Error Drive

30H TSW ACT/STBY Changeover Failure

➁ Active TSW No

➂ -➅MUX card ACT-side linkage condition

➆ -➉MUX card Stby linkage condition B7 b6 b5 b4 b3 b2 b1 b0

31H TSW ACT/STBY Changeover Failure MUX Fault

Detected Error Item

Active TSW No

MUX card ACT-side linkage condition B7 b6 b5 b4 b3 b2 b1 b0

➆ -➉MUX card Stby linkage condition B7 b6 b5 b4 b3 b2 b1 b0

41H CPU ACT/STBY Changeover Failure

Diagnosis

42H CPU ACT/STBY Changeover Failure

43H CPU ACT/STBY Changeover Failure PCI Fault

➁ ACT system after changeover

50H Trunk Ineffective Hold Detected

Diagnosis ➁ Lens of Trunk Ineffective Hold MG, U

➂ Lens of Ineffective Hold Trunk G, LV

➄ ➅ ➆ ➇ ➈ 11➉12

51H Trunk Ineffective Hold Detected and Released

52H Trunk Ineffective Hold Detected Impossible

70H Call Forwarding Memory Clear NG

Was stopped

A0H Periodic Backup Abnormal End

Error detection by Routine

Diagnosis Information of Periodic Backup

Abnormal End

Refer to No. ➂ Refer to No.➃ Refer to No.➄

➁ ED Error Data

C0H Detection of Remaining Link Abnormal End

PLO MB Key Turn on

PLO MB Key Turn OFF

➀ Location of faulty CCH/DCH card

13-A CCH Clock Failure

13-B

CCH C-Level Infinite Loop Failure Permanent

13-C CCH C-Level Infinite Loop Failure Temporary

13-D

CCH Lock-Up Failure Permanent

13-E CCH Lock-Up Failure Temporary

13-F

CCH B-Level Infinite Loop Failure Permanent

13-G CCH B-Level Infinite Loop Failure Temporary

13-H

CCS Link Failure Permanent

➁ Data Analyzed by NEC Engineers

Ccitt Factor Error

➂ Probable cause for failure

13-I

CCS Link Failure Temporary

FLT ID Ccitt Factor Error

➂ Probable cause for the failure

➁ CKT No. of faulty circuit

13-J

Restoration From CCS Link Failure

13-K CCH Reset Interrupt Failure

This message displays when a digital line failure occurs

➁ Kind of Fault B7b4 b3 b2 b1 b0

13-N

➀ Accommodated location B7 b6 b5 b4 b3 b2 b1 b0

13-O Digital Line Failure

13-P

13-Q DRU Battery Operation

➀ Accommodated location

13-R

DRU Line Operation

➀ Accommodated location

13-Z Power Failure

➀ MG No. and Unit No. of fault detection

➁ Kind of Power

➂ Location of faulty circuit card

This message displays when a VPS failure is detected

15-A

VPS Failure Temporary

➁ Lens of VPS with the failure

15-B VPS Failure Permanent

VPS Restore

15-C

➀ Lens of VPS with the failure

16-A Inside Trunk All Busy

➀ Intra-Office trunks that have

Become all busy

Route

Trunk Name Route

Trunk Name

16-B Virtual Tie Line Set Report

➁ Virtual Tie Line Call Header

Accommodated Location

➂ Virtual Tie Line Call Header

Virtual Tie Line Cancel Report

16-C

16-E Virtual Tie Line Set Time Out

➀ Virtual Tie Line Call Header

Call Source

Reason Class Kind Data Reason Kind Value

Invalid message class

System Messages Reason Class Kind Data Reason Kind Value

16-F

Sender Start Time Out

Case of Station OG/ATT OG/ATT Tandem Connection

➄ Tenant No. of calling station Hex. b7 OP data 0/1

➅ Optn data

➆ OG route number Hex B7 b6 b5 b4 b3 b2 b1 b0

➇ Oprt data

➈ Trunk No. of OG trunk

➉ Trunk No. of sender

Number of digits dialed by caller

Number dialed by caller See table B6 b5 b4 b3 b2 b1

Case of Tandem Connection

➀ Type of connection

➁ IC route number Hex

➂ Oprt data

➇ Oprt data

Number dialed by caller See table B7 b6 b5 b4 b3 b2 b1 b0

➀ Faulty Port No

16-K Port Line OFF

IOC0 IOC1

Port Line Restore

16-L

16-M Hard Clock Failure

Hard Clock Restore

16-N

This message displays when the IOC card fails

➁ Cause for fault

16-T IOC Failure Temporary

16-U

IOC Failure Permanent

➀ Error code

Error Code HEX Failure

16-X Station Exchanged Report

➁ Tenant No. of calling station

B4-b7 B0-b3

17-A

CCH MBR Key Turn on

➀ Location of CCH/DCH card B7 b6 b5 b4 b3 b2 b1 b0

➁ CKT No

17-B CCH MBR Key Turn OFF

17-C

CCH MB Key Turn on

➀ Location of CCH/DCH card

17-D CCH MB Key Turn OFF

17-H

Day/Night Change Information

➀ Tenant No B7 b6 b5 b4 b3 b2 b1 b0 ➁ Changing Method

Night Mode 2 available only for Japan

17-O

IOC MB Key Turn on

17-P IOC MB Key Turn OFF

17-Q

IOC MBR Key Turn on

17-R IOC MBR Key Turn OFF

23-P

DCH Back-Up Automatic Change Start/End

➀ Condition of Dch

System Messages

23-Q

DCH Back-Up Manual Change Start/End

System Messages

23-Y

MUX Clock Failure

➁ Scan Data

23-Z Both MUX Clock Failure

➀ MUX card location

➂ Scan Data

This message displays when the MAT is log-in or log-out

26-N

MAT Log

➀ Port No. of the MAT logged in/out b0-b2 I/O Port No

When a call is originated from a station

26-R Call Trace

➃ User Group No. UGN Hex

➉ User Group No. UGN Hex

Output Data Hex Actual Meaning Blank

When a call is originated from a trunk

Information on Called Party Informer

Detailed meanings are as follows

26-V LAN Interface Error Report

➀ ➁ ➂ ➃ ➄ ➅ ➇➆

Error Code Output Data Definition Hex

Kind of Error

Details on Detected Error

Not used

When 9 =05 OAI / 07 MIS

12 ~ 24 Not used

26-W LAN Interface Release Report

When ➈=03 Smdr / 04 MCI

➉ Device Number of recovered client PC Recovery Information

➈ Application Type

33-A MUX Clock Restore

➁ RLS Data

SDT Alarm Warning

➁ Details on alarm

33-B

➀ MG Module Group

➂ Alarm-detected HW

Repair Procedure

=-/VC-11 Path Trouble

SDT Alarm Trouble

33-C

Repair Procedure

NDA-24300CHAPTER

33-D SDT Alarm Restore

➁ Details on the fault

33-E

SDT Interface Change Notify

➁ Detailed information

This page is for your notes

Unit/Circuit Card Replacement Procedure

LPM Accommodating Unit/Circuit Card Replacement Procedure

Precaution

Circuit Card Mounting Face Layout

UNIT/CIRCUIT Card Replacement Procedure

LANIPZ-PC19 GATEPZ-GT16

Operating Procedures

UNIT/CIRCUIT Card Reference Item Remarks

CPR Replacement Procedure

PZ-IO27 Note

How to Replace the CPU

Circuit Card Accommodation into the New CPR

Removal of Front Panel and Top Cover from CPR

Isagt PZ-GT13

Lani PZ-PC19

Reattachment of CPR Top Cover and Front Panel

Accommodation of New CPR into LPM

By using the two screws, fasten the new HFD onto the CPR

Insertion of New HFD into CPR

Replacement Procedure

Refer to -2for CPR face layout Refer to -3to replace the CPU

Section

Palm connector yet

EMA SUP lamp on the EMA card goes OFF

IMG0 lamp on the DSP flashes

Top Cover Front Panel

10 Insertion of Isagt and Lani Cards

11 Reattachment of CPR Top Cover and Front Panel

LPM

CPR

EMA Card Replacement Procedure

13 Insertion of New HFD Into CPR

YES

END

IOC Card Replacement Procedure

Replacement Procedure

OPE lamp on the IOC card goes

UNIT/CIRCUIT Card Replacement Procedure

Power Supply Unit Replacement Procedure

CPU System Changeover Refer to .1.2 in Chapter

UNIT/CIRCUIT Card Replacement Procedure

Misc Card Replacement Procedure

Keep MB switch UP

Tswm Accommodating Circuit Card Replacement Procedure

ALM RST button is used to reset the alarm lamps only

Circuit Card Reference Item Remarks Function Name

GT Card Replacement Procedure

Misc BUS

GT Card Replacement Procedure

System changeover of GT from ACT to Stby mode

CPU OPE CPU DSP = OFF

UNIT/CIRCUIT Card Replacement Procedure

IMG0 CPU DSP = Flash green IMG1-3 CPU DSP = OFF

TSW Card Replacement Procedure

16 System Block Diagram TSW and Other Speech Path Echelons

TSW Card Replacement Procedure

Use extreme care when operating the keys on the circuit card

UNIT/CIRCUIT Card Replacement Procedure

TSW ACT lamp on the new card goes OFF

TSW ACT lamp on the new card

Remains OFF

They are all steady-green

Dlkc Card Replacement Procedure

Refer to -16and Figure

PLO Card Replacement Procedure

OFF

OPE lamp on the new card is OFF

PWR SW Card Replacement Procedure

Misc Card Replacement Procedure

PIM Accommodating Circuit Card Replacement Procedure

18 Circuit Card Mounting Face Layout of PIM

Circuit Card Reference Item Remarks Function Name

1 LC/TRK Circuit Card Replacement Procedure

Keep MB switch set at UP

MUX Card Replacement Procedure

MUX ACT lamp on the new card is red

Refer to -16and Figure

SDT Card Replacement Procedure

Procedure to Replace Optical Fiber Cable

OPE lamp on the PA-SDTA card is steady-green

Procedure to Replace PA-SDTA/PA-SDTB card

UNIT/CIRCUIT Card Replacement Procedure

OPE lamp on the new card is red

Green

PWR Card Replacement Procedure

OPE lamp on the card goes OFF

UNIT/CIRCUIT Card Replacement Procedure

Fan Unit Replacement

Replacement Procedure Fanu on Topu

20 Preparation for Fanu Replacement Fans on Topu

21 How to Replace Fanu Fans on Topu

Replacement Procedure Fanu in Fan Box

OFF

23 How to Replace Fanu Fans in Fan Box

CPR Cooling Fan Replacement

PZ-IO27 PZ-GT16 and PZ-GT13 Isagt

25 Extraction of CPR from LPM

27 How to Remove the Cooling FAN

Fuse Replacement

28 Fuses Used by System

30 Fuse Locations Within System

31 Fuse Location Within Tswm

32 RGU Fuse Blown Fault Flowchart

33 DC -48V Fuse Blown Fault Flowchart

Fault Repair Procedures

Faulty Item Faulty Situation Reference Section

Fault Repair Procedures

Fan Unit Fault

Line Fault

Faulty Situation Reference Section

Check Point

Line Control

Line Fault When Dial Tone DT Cannot Be Heard

Check the faulty line on the MDF

Line Fault When Dialing Results in Wrong Connection

Line Fault When Bell Does Not Ring

When Call Cannot Be Answered and Speech Cannot Be Made

Dterm Fault

END

Trunk Fault

Trunk Faulty Situation Reference Section

Timings for Trunks

Timings for Senders

Trunk Control

Controlling Trunk Circuit Cards and Speech Path

Trunk ORT, SND, CFT Fault

Trunk COT, TLT, DTI Fault

Replace the Dterm with a spare

TLT

RA RB TA TB

ATTCON/DESKCON Fault

ATTCON/DESKCON Control

ATT Connector Cabling and Connector Leads Accommodation

ATTCON/DESKCON Fault

Replace the ATTCON/DESKCON with a spare

ATTCON/DESKCON

Unit Fault

Fault Situation Reference Section

Unit Control Block Diagram Dual Configuration

Unit Control Block Diagram Single Configuration

Unit Fault Fault Related to Speech

END

For Single Configuration

END

Unit Fault When Dial Tone DT Cannot Be Heard

Circuit card UP and extract

For Single Configuration

Circuit card UP and extract

Start

If the connection is set up, set

Faulty system into Stby

Replace the MUX circuit card with a

Spare, and check it

Speech Path TSW System Fault

Faulty Situation Reference Section

Speech Path Block Diagram

IMG2 PIM

Speech Path System Fault Fault Related to Speech

TSW Write Failure For Dual Configuration

END

For Single Configuration

END

Speech Path System Fault When Dial Tone DT Cannot Be Heard

Speech Path System Fault Stby Side Has Become Faulty

END

Control System Fault

CPR TSW MUX

EMA circuit cards

CPU Controlling Block Diagram

Lani Isagt

Control System Fault Fault Occurs Intermittently

END

Control System Fault Stby Side Is Faulty

10 Alarm Bus Cable Connections Diagram

IMG

Alarm Indication Fault

Fault of Alarm Indicating Panel

11 Cable Routing for Alarm Indications

Fault That Cannot Be Detected

Power Supply Fault

System configuration

System configuration

16shows the power supply system for PIM

18shows the power supply system for Tswm

Fuse Blown Fault

Circuit Breaker OFF Fault in PWR Supply

Fault of Alarm Lamps on PWR Supply

Fault Supervision

FAN Unit Fault

19 Circuit Diagram of Fan Unit and Thermal Unit

Fan Unit Fault

PIM

If the voltage is -48

Tone Fault

20 Dial Tone Connection

Tone Fault

21 External Hold Tone Supply Block Diagram

System Down Fault

22 System Down Fault Repair Sequence

When Cause for Fault Cannot Be Identified

END

When Faulty Circuit Cards Can Be Assumed From System Message

Common Channel Interoffice Signaling Ccis Line Fault

Ccis Line Control

Specific CCH/CCT Card Is Faulty

Check by replacing CCH/CCT card with a spare

Fault of CCH, DTI and Related Flat Cable

Integrated Service Digital Network Isdn Line Fault

Isdn Line Control

Specific DCH/PRT Card Is Faulty

Check by replacing the DCH/PRT card with a spare

Fault of DCH, DTI, and Related Flat Cable

Hard Time Clock Fault

Start END

This page is for your notes

Alarm Indications

Kinds of Alarm Indications

How to Stop Alarm Indications

Alarm Indications on Topu

Lamp Color Function Contents

System Operations

Variable Alarm Indication

Command Command Full Name

Collection of System Messages

Automatic Printout to System Message Dedicated Printer

Recovery Procedure

Display on MAT

Indication of Lockout Stations

Indicating Method

Rlst

Operating Procedure

Line Load Control

Cancelling

Line Load Control Operations on ATTCON-Cancelling

Line Load Control Key Operations on DESKCON-Setting

11 Line Load Control Indication Deskcon

Message Content

IOC Line Monitor

Make-Busy/Make-Busy Cancel of Station and Data Terminal

Line Management

Make-Busy/Make-Busy Cancel of C.O. Line/Tie Line

Class Change and Number Change of Station and Data Terminal

Line Management Commands

Station Message Detail Recording System Smdr

Transmission Data to Smdr Equipment

Ascii Code Charac Binary Digit Remarks TER HEX

14 Message Format for Outgoing Call

15 Message Format for Incoming Call

16 Message Format for Station-to-Station Call

For an Attendant Orig = 1 Data showing Attendant Number

Call Start/Call End Time Information

Data which indicates Call Start Time is as follows

Data which indicates Call End Time is as follows

Called Number

Data which indicates the Called Number is as follows

Account Code/Authorization Code

Data which indicates the Authorization Code is as follows

Data which indicates the Account Code is as follows

Route Advance Information

Condition B Information

Call Metering Information

Kind Contents Outgoing Incoming

Text Format of Centralized Billing Fusion

System Operations

17 Message Format for Outgoing Call Fusion

18 Message Format for Incoming Call Fusion

19 Message Format for Station-to-Station Call Fusion

Reference

Data = 02 Calling Party Information Station Number

Data = 08 Condition B Information

FPC1

Data = 16 Automatic Number Indication

Attcon

Text Format of Smdr TCP/IP Interface

Text sending direction Client Server

Xxxxx

Traffic Management

Kind of Traffic Measurement

5shows the kinds of traffic measurements

Type Kind Description Measurement

Deskcon

Operating Procedure

Step Asyd Asydn Atrf

Atrfn

21 IPX MAT Menu Display Image Example

Data Output Details on DTFD/DTFDN Command

Full Command Name

Name

Data collecting Log

Tool Buttons Collect Data

Stop

Print Log

Display Area

Save Text File

Down

System Operations

Office Data Management

Office Data Stored Locations

Office Data Preservation

Office Data Management Procedure

25 Office Data Change Procedure

26 Office Data Change Procedure

27 Backup Commands

Individual Speed Calling Data Hddmat command

Data Management Commands

One-Touch Speed Call Memory Data Management

Test Operations of Various Kinds

Dcon

Test Item Content of Confirmation Remarks

Designated Connection Test Station

Designated Connection Test Procedure Register Test Procedure

Sender Test Procedure

SRV=SSC, SID=17

Party Conference Trunk Test Procedure

31 3-Party Conference Test Procedure

32 3-Party Conference Test Connection Diagram

Tone Test Procedure

33 Tone Test Procedure/Connection Diagram

Tone no Kind of Tone Remarks

Interrupt Ringing IR Test Procedure

34 Interrupt Ringing IR Test Procedure/Connection Diagram

Trunk Test Procedure

35 Trunk Test Procedure

36 Trunk Test Connection Diagram

Designated Connection Test DESKCON/ATTCON

Trunk seizure by access code dialing

Bad Call Notification

Spdt

Routine Diagnosis

Related System Data

ASYD, SYS1, INDEX86

INDEX89

INDEX90

INDEX304

Call Forwarding Data Clear See Index

HDD see Index

Routine Diagnosis Result

System Control Procedures

Belonging Isagt and LANI, are also changed over

37 Switching Network General Block Diagram

Does not affect any other systems

38 How to Check LEDs and SW Keys for System Changeover IMG0

39 How to Check LEDs and SW Keys for System Changeover IMG1

IMG 2/3

41 How to Check Status LEDs

How to Control CPU Block

Type Operations Remarks

42 System Block Diagram Switching Network Between CPU and GT

Manual System Changeover of CPU

DSP Front View

45 CPU Changeover via MBR Key

Forced Changeover of CPU

LANIPZ-PC19 ISAGTPZ-GT13

How to Control Switching Block

Changeover of Switching Block Type Operations Remarks

Manual System Changeover of Speech Path System

Dlkc PLO CPR Isagt CPU Lani Isagt PZ-GT13 Lani PZ-PC19

49 TSW/DLKC/MUX in ACT Mode

51 Speech Path System Changeover via Active GT MBR Key

53 Check of Active PLO

54 PLO in ACT/STBY Mode

Manual System Changeover of PLO

Flip the MB key on the PLO card. Refer to Figure

55 PLO Changeover via MB Key

Initialization General

System Initialization by Turning on Power Supply

CPU DSP#0

CPU DSP#1 IMG0

System Initialization by Key Operations on Topu

Type Description

57 Conceptional Diagram of Initial Program Load

58 Related Keys and LEDs for System Initialization

Program KEY NON Load

System Data KEY NON Load

END ON. on Line

System Data KEY Load

DSP of active CPU Is ON. on Line

Program KEY Load

Program KEY Load

Active CPU light steadily green

System Data KEY → NON Load

System Initialization by Keys on CPU Front Panel

Start EMA PH-PC40

Check ACT0/ACT1

Lamps on the EMA

System Initialization by Sinz Command

Return MB switch to

Previous position after

MB lamp has turned on

How to Turn ON/OFF Whole System

How to Turn On Whole System

How to Turn OFF Whole System

60 How To Turn OFF the Whole System

Have already been installed in the HD. Office Data has not

Been installed

Procedure #2 see Table

Office Data have been already installed in the HD

➀ When Power is OFF ➁ When Power is on OFF Line

Set Sense switch at 1 DM

Line

On Line

Set Sense switch at 2 DM Load Restart on the DSP of active

CPU

Set the Sense switch at

DM Load Restart on the DSP

On Line END

This page is for your notes

Routine Maintenance Procedure

Flow of Procedures

1shows the tools and equipment required for test procedures

Routine Maintenance Procedure

Required Test Equipment and Tools

Test EQUIPMENT/TOOLS Purpose Remarks

Routine Maintenance Procedures

Time Procedure Reference Section Remarks

Ambient Conditions in Switch Room Check

Alarm Check

MAT/Printer Check

Collection of System Messages

Display of Locked-out Station

Refer to , Fan Unit Fault, in Chapter

Fan Unit Check

Alarm Tests

Main Power System Check

Trunk RGU Check

ATTCON/DESKCON Check

Attendant Console Check

Desk Console Check

PM WED

System Check

Routine Maintenance Check Lists

Condition And Cause Procedure and Parts Used

Test Type Test Item Connection Diagram

Connection test diagrammed to

Trunk/Tie Line

Right Connection Test-ATTCON/DESKCON

Register/Sender Trunk RST

ORT Function Perform the test by specifying

DP/PB

RST

Function

Trunk no Sender

SND0

Digital Conference Function

Message displays as a result Test

Function Speech Release Remarks Trunk no

Speech Path for Each PIM, and Ringing Generator Unit

That the station rings

Mounting Location Check

Module Name Unit Name

PIM1 PIM2 PIM3 PIM4

Test Item Connection Diagram

Attendant Console ATTCON/DESKCON

Deskcon

Call Termination Call Origination

Attcon

Speech Release Deskcon no

Maintenance Commands

Maintenance Commands

Dteln

Maintenance Commands

Allc Assignment of Line Load Control

Functional Outline

Parameters

Almg Assignment of Alarm Grade Data

LMP

GRD

Type

Atrf Assignment of Traffic Measurement Order

Functional Outline

Bosd Back Up One-Touch Speed Call Memory Data

Cadsd Continuous Assignment of Station Data

Example Input data

STNEND=200

Result

TEC

=DP/PB

RSC

SFC

When Delete is selected in the Type selection list box

Carr Continuous Assignment of Alternative Route Restriction

IC Lgrt START/END

IC Lgrt

OG Lgrt

When Assign is selected in the Type/KIND selection list box

Catk Continuous Assignment of Trunk Data

TKEND=21

Data Entry Result

When Delete is selected in the Type/KIND selection list box

Tkstart

Tkend

Details on Trunk Arrangement Type

TYPE=1 Level →

TYPE=3 Group →

TYPE=5 Unit →

Chapter

Cbcn Control of Broadcasting for NDM

FPC

FPC of the designated Node Note

Interval Broadcasting Interval

Ccse Change of Common Signaling Channel Equipment

CCH Lens

MG=XX, UNIT=X, GROUP=XX

Link

Cdbu Change of Dch Backup

CNT

STS0

STS1

Cmod Change of System Mode

Device

=CPU =TSW

System

Cmwl Control Message Waiting Lamp

Cmwlt Control Message Waiting Lamps Telephone Number

UGN

Teln

Cprs Controlled Alternate PRSCs

Priority Restriction Class N/U

=Normal

=Urgent

Cscl Continuous Change of Station Class

Cstn Continuous Change of Station Number

Dcbd Display of Call Block Entry Data

NDA-24300CHAPTER

Dcen Display of Connection Trunk Lens Data for LDM

Clens

CRT

CTK

Dcon Display of Connection Status

LEN CRT

Connection Route Number 1-1023 Note

Connection Trunk Number 1-4095 Note

Dftd Display of System Message Details

Input data New/Old Show Details YES/NO

Diss Display of Program Issue

Version Issue Date Group 00-23 SP No Digits Ascii 2 digits

Dlen Display of Lens Data

Room Class ANX

=Ground

=Underground

FLR

Floor

This command prints the Lens of stations in lockout state

Dlsl Display of Lockout Station Lens

Dlss Display of Lockout Station Number

STN Lens

Dlsst Display of Lock Out Station Number Telephone Number

Count

Telephone Number max digits

Dltel Display of Telephone Number from Lens for LDM

Station Number Max digits

Dntel Display of Telephone Number from Lens for NDM

NID

Network ID Note

Telephone Equipment Number

Dpkg Display of Setting Port Package

Input Data Module Group MG number

Unit U number

Dpsw Display Package Switch Status

Kind

PMN

PKG Name

Dstn Display of Station Data

Dteln Display of Telephone Number Data for NDM

Cpgn

Cpen

Shun

Shcn

DTF101 Display of Terminal Traffic Data

DTF102 Display of Route Traffic Data

DTF103 Display of Station Peg Count Data

DTF104 Display of Attendant Peg Count Data

DTF105 Display of Route Peg Count Data

DTF201 Display of Service Peg Count Data

DTF301 Display of UCD Route Peg Count Data

DTF302 Display of UCD Group Peg Count Data

DTF303 Display of Station Peg Count Data

DTF501 Display of Attendant Answering Peg Count Data

DTF601 Display of Connection Route Peg Count Data

DTF602 Display of Connection Route Traffic Data

DTF101N Display of Terminal Traffic Data for Fusion Network

DTF102N Display of Route Traffic Data for Fusion Network

DTF103N Display of Station Peg Count Data for Fusion Network

Functional Outline

DTF105N Display of Route Peg Count Data for Fusion Network

DTF201N Display of Service Peg Count Data for Fusion Network

Functional Outline

Functional Outline

Functional Outline

Functional Outline

Functional Outline

Functional Outline

Flinst File Install

Data Install Procedure

Hddfdd Data Control Between HDD and FDD

Input data System Select

HFD0/HFD1

File Name Select Auto Verify Afterward

Hddmat Data Control Between HDD and MAT

Hddmatn Data Control Between HDD and MAT for NDM

Hdfp HDD Format of PBX

Mbct Make Busy of Connection Trunk for LDM

Make Busy Information 0/1

=Make Busy Outgoing

Mble Make Busy of Lens

=Make Busy

Mbpm Make Busy of Port Microprocessor

Input data MG Unit Group Display data =Make Idle =Make Busy

Mbrt Make Busy of Route

Mbrtlr Make Busy of Route-Logical Route Number

Lgrt

Mand as to the Internal route number and its meaning. Note

Make Idle

Mbsm Make Busy of System Message Printout

Port no

This command assigns the Idle/Busy status of stations

Mbst Make Busy of Station

Exit Click to exit this command

Mbstt Make Busy of Station Telephone Number

Make Busy/Make Idle Display Data

Mbtc Make Busy of Trunk-Continuous

Mbtclr Make Busy of Trunk-Continuous-Logical Route Number

Logical route number allocated to the Route Number. Note

Trunk Number Note

=Make Busy Bothway Note

This command assigns the Idle/Busy status of trunks

Mbtk Make Busy of Trunk

Mbtklr Make Busy Trunk-Logical Route Number

Memhdd Data Control Between Memory and HDD

Memhddn Data Control Between Memory and HDD for NDM

Input data Direction Select MEM to HDD

Mfch Make Busy of Fcch

Fchn

FCH Number

Pmbu Port Microprocessor Back Up

Nating Port Microprocessor to MAT

Ralm Release Alarm

This command clears the fault indications

Ralmn Release Alarm for NDM

Status Result of releasing the alarm

OK/NG

Rlst Release Station/Trunk

=LENS

Information

Rlstt Release of Station/Trunk Telephone Number

Telephone Number Trunk

Connection Trunk

External/Internal Route Number Trunk Number

ERN

GRN

CSN/ZTN

PCN

Sinz System Initialization

Kind of Initialization

=System Initialize

=System Initialize Office Data Load & System Initialize

Spts Scanning of Port Status

Type 1 By MG

Type of Circuit Card Function Name

Exit

Type 2 By MG, Unit

Port Status Report MG, Unit Display

Type 3 By MG, Unit, Group

Display of Scanning by Designating Group

Idle = Idle

= Unassigned Port

TCL

Trunk Class

Srts Scanning of Route Status

Srtslr Scanning of Route Status-Logical Route Number

Interval Interval Time of two scan Display Data

Route of Route Number

Number of Idle/Busy TK

Xhfd X-RAY HD or FDD Diagnosis

Function

Area

Fault Drive

Fault Sector

Message

![]()

![]() MEMORY

MEMORY