FPGA Registers | Maps and Registers |

|

|

FPGA Registers

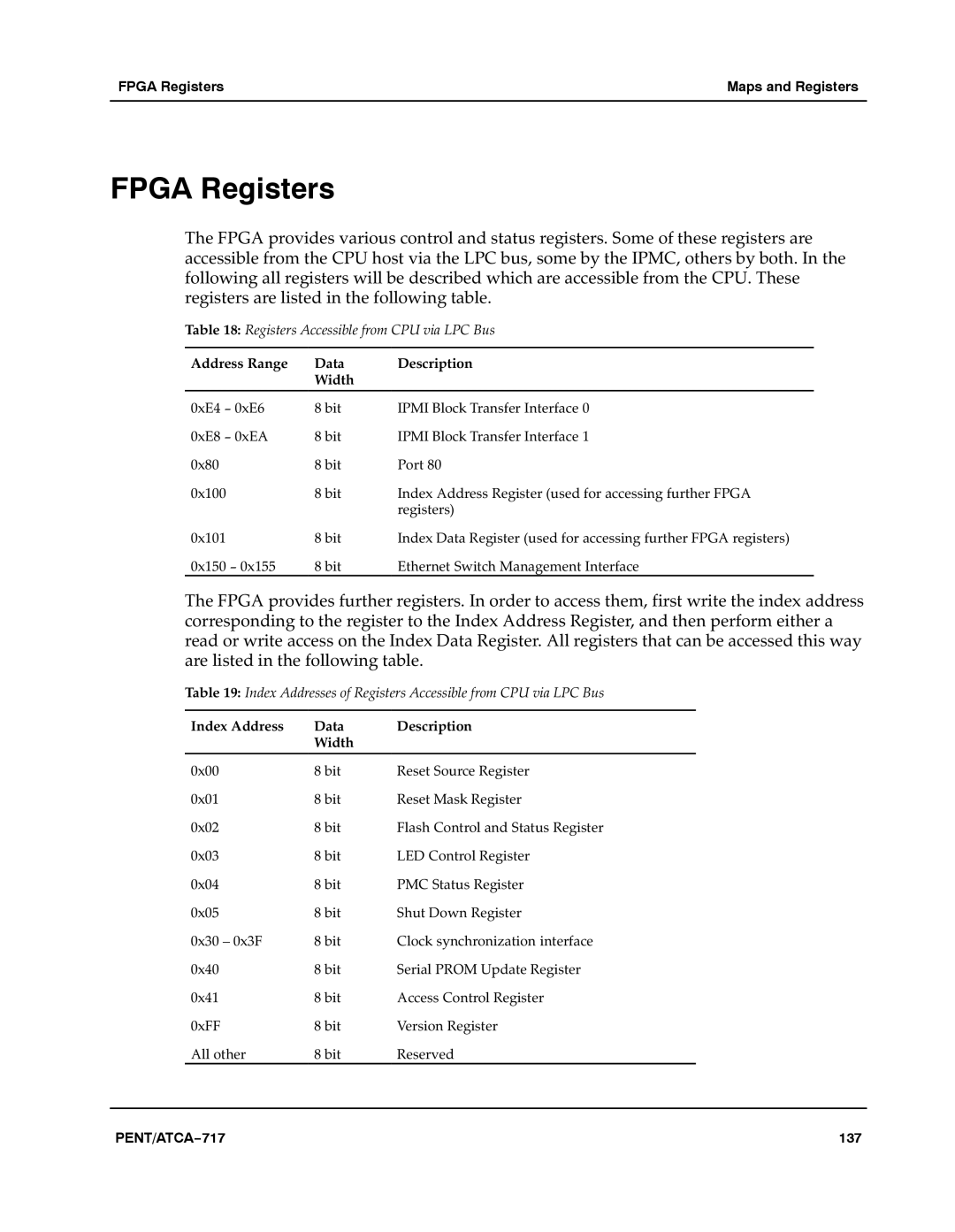

The FPGA provides various control and status registers. Some of these registers are accessible from the CPU host via the LPC bus, some by the IPMC, others by both. In the following all registers will be described which are accessible from the CPU. These registers are listed in the following table.aaa

Table 18: Registers Accessible from CPU via LPC Bus

Address Range | Data | Description |

| Width |

|

|

|

|

0xE4 − 0xE6 | 8 bit | IPMI Block Transfer Interface 0 |

0xE8 − 0xEA | 8 bit | IPMI Block Transfer Interface 1 |

0x80 | 8 bit | Port 80 |

0x100 | 8 bit | Index Address Register (used for accessing further FPGA |

|

| registers)a |

0x101 | 8 bit | Index Data Register (used for accessing further FPGA registers) |

0x150 − 0x155 | 8 bit | Ethernet Switch Management Interface |

The FPGA provides further registers. In order to access them, first write the index address corresponding to the register to the Index Address Register, and then perform either a read or write access on the Index Data Register. All registers that can be accessed this way are listed in the following table.a

Table 19: Index Addresses of Registers Accessible from CPU via LPC Bus

Index Address | Data | Description |

| Width |

|

|

|

|

0x00 | 8 bit | Reset Source Register |

0x01 | 8 bit | Reset Mask Register |

0x02 | 8 bit | Flash Control and Status Register |

0x03 | 8 bit | LED Control Register |

0x04 | 8 bit | PMC Status Register |

0x05 | 8 bit | Shut Down Register |

0x30 – 0x3F | 8 bit | Clock synchronization interface |

0x40 | 8 bit | Serial PROM Update Register |

0x41 | 8 bit | Access Control Register |

0xFF | 8 bit | Version Register |

All other | 8 bit | Reserved |

PENT/ATCA−717 | 137 |