Maps and Registers | FPGA Registers |

|

|

Clock Synchronization Interface Registers

These registers are related to the clock synchronization building block of the blade. These registers are primarily used to:aa

SSelect system clock 1 or 2 from back plane

SSelect system or reference clock for DPLL input

SEnable reference clocks A and B to the backplane

SSelect recovered clock source

SDetermine programmable reference clock divider value

SDetermine reference clock pulse width

Note:aMotorola offers a device driver to access the clock synchronization interface. Instead of directly accessing the clock synchronization interface via the registers described in this section, it is strongly recommended to use this driver. Ask your local Motorola representative for details.a

The following clock synchronisation interface registers are available:

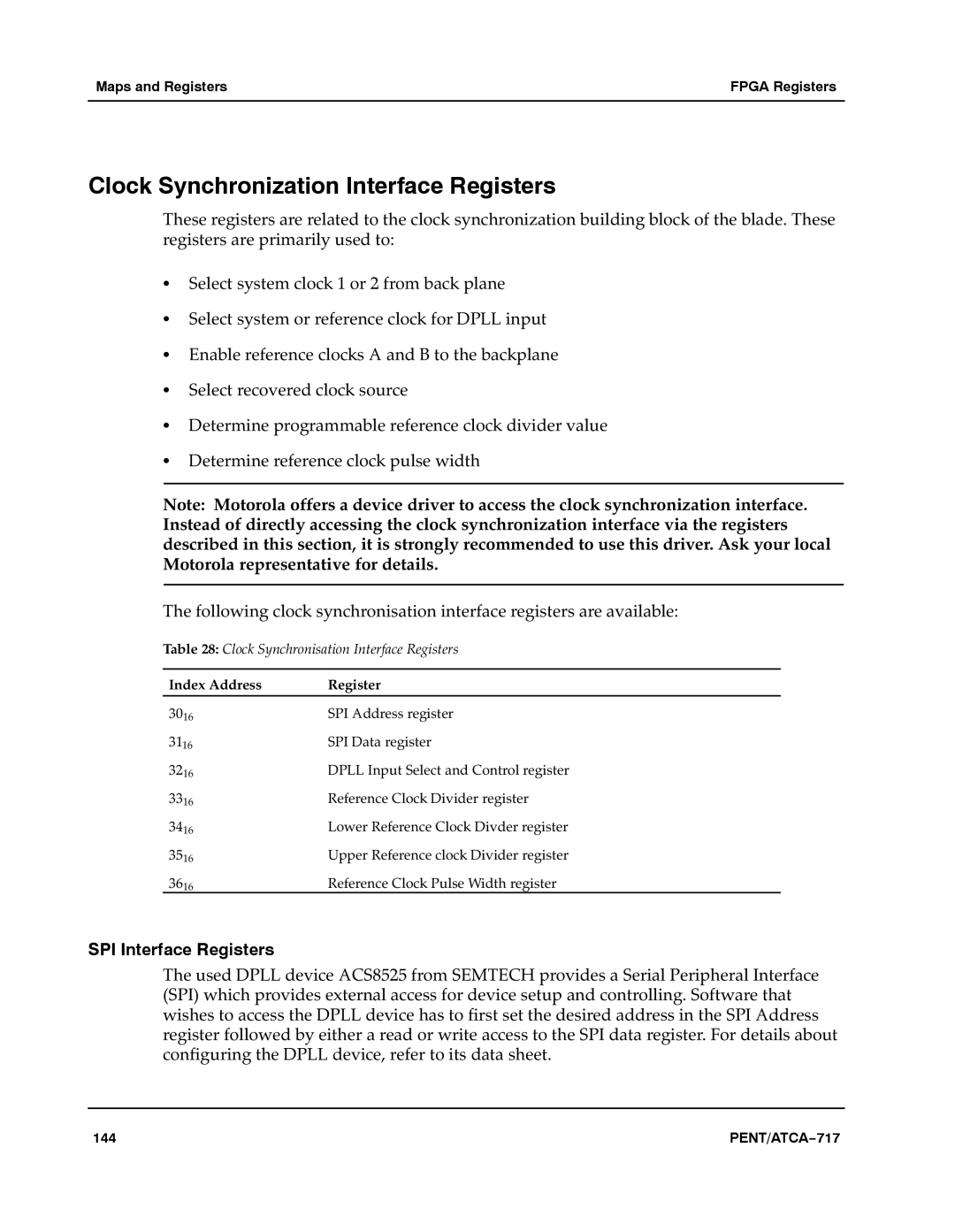

Table 28: Clock Synchronisation Interface Registers

Index Address | Register |

3016 | SPI Address register |

3116 | SPI Data register |

3216 | DPLL Input Select and Control register |

3316 | Reference Clock Divider register |

3416 | Lower Reference Clock Divder register |

3516 | Upper Reference clock Divider register |

3616 | Reference Clock Pulse Width register |

SPI Interface Registers

The used DPLL device ACS8525 from SEMTECH provides a Serial Peripheral Interface (SPI) which provides external access for device setup and controlling. Software that wishes to access the DPLL device has to first set the desired address in the SPI Address register followed by either a read or write access to the SPI data register. For details about configuring the DPLL device, refer to its data sheet.a

144 | PENT/ATCA−717 |