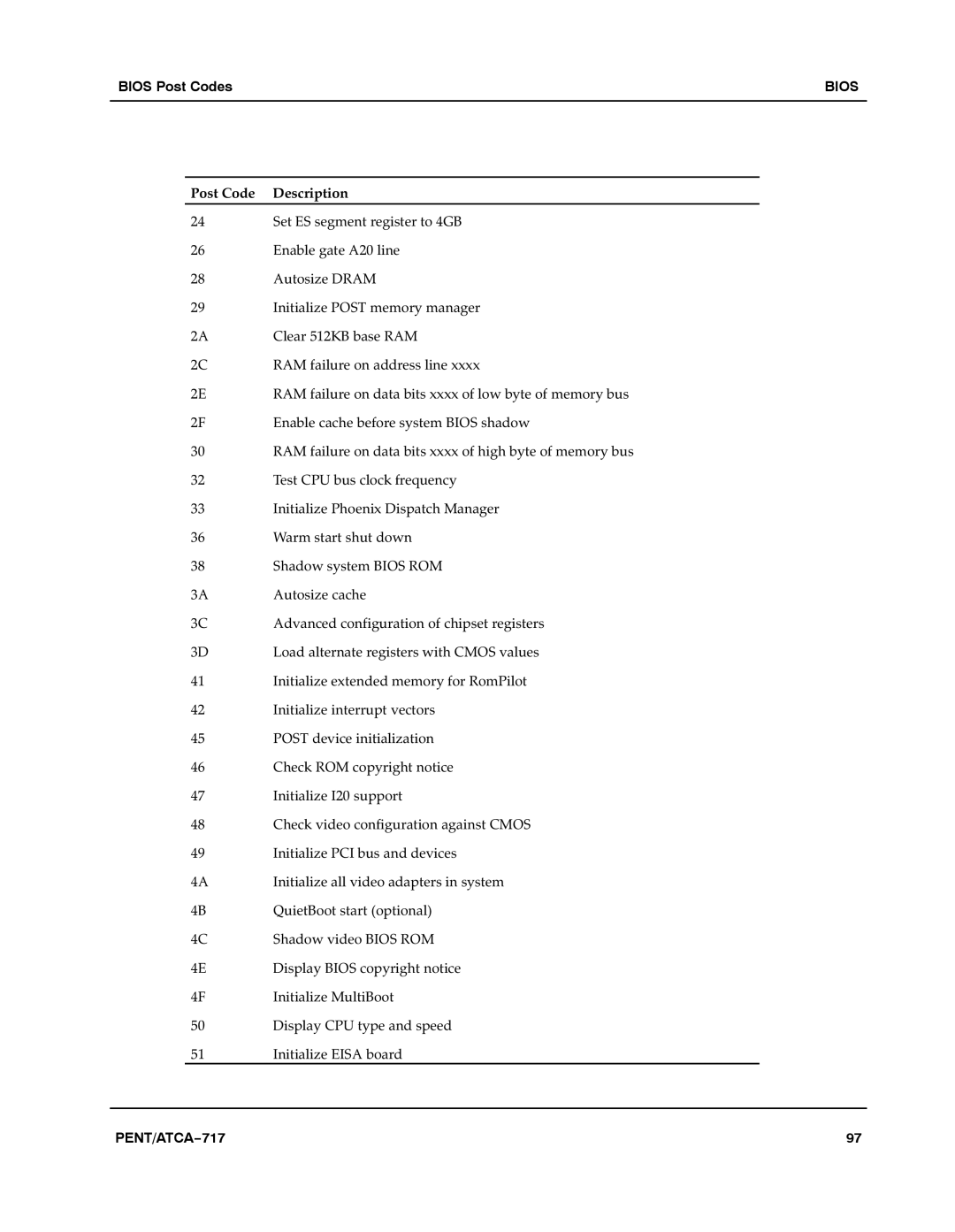

BIOS Post Codes | BIOS |

|

|

Post Code | Description |

24 | Set ES segment register to 4GB |

26 | Enable gate A20 line |

28Autosize DRAM

29Initialize POST memory manager

2A | Clear 512KB base RAM |

2C | RAM failure on address line xxxx |

2E | RAM failure on data bits xxxx of low byte of memory bus |

2F | Enable cache before system BIOS shadow |

30 | RAM failure on data bits xxxx of high byte of memory bus |

32Test CPU bus clock frequency

33Initialize Phoenix Dispatch Manager

36 | Warm start shut down |

38 | Shadow system BIOS ROM |

3A | Autosize cache |

3C | Advanced configuration of chipset registers |

3D | Load alternate registers with CMOS values |

41Initialize extended memory for RomPilot

42Initialize interrupt vectors

45POST device initialization

46Check ROM copyright notice

47Initialize I20 support

48Check video configuration against CMOS

49Initialize PCI bus and devices

4A | Initialize all video adapters in system |

4B | QuietBoot start (optional) |

4C | Shadow video BIOS ROM |

4E | Display BIOS copyright notice |

4F | Initialize MultiBoot |

50Display CPU type and speed

51Initialize EISA board

PENT/ATCA−717 | 97 |