FPGA Registers | Maps and Registers |

|

|

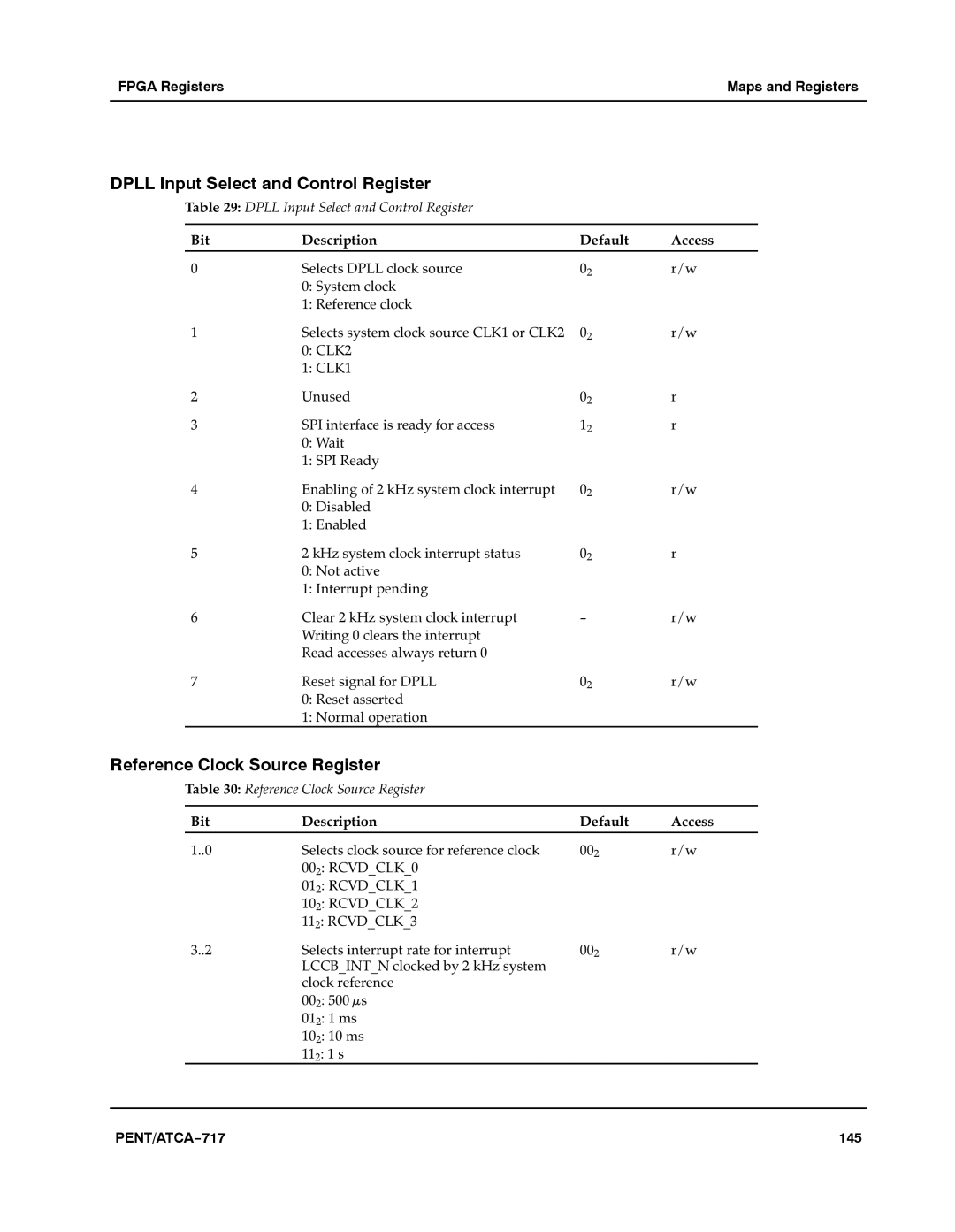

DPLL Input Select and Control Register

Table 29: DPLL Input Select and Control Register

Bit | Description | Default | Access |

0 | Selects DPLL clock sourcea | 02 | r/w |

| 0: System clock |

|

|

| 1: Reference clock |

|

|

1 | Selects system clock source CLK1 or CLK2 | 02 | r/w |

| 0: CLK2 |

|

|

| 1: CLK1 |

|

|

2 | Unused | 02 | r |

3 | SPI interface is ready for access | 12 | r |

| 0: Wait |

|

|

| 1: SPI Ready |

|

|

4 | Enabling of 2 kHz system clock interrupt | 02 | r/w |

| 0: Disabled |

|

|

| 1: Enabled |

|

|

5 | 2 kHz system clock interrupt status | 02 | r |

| 0: Not active |

|

|

| 1: Interrupt pending |

|

|

6 | Clear 2 kHz system clock interrupt | − | r/w |

| Writing 0 clears the interrupt |

|

|

| Read accesses always return 0 |

|

|

7 | Reset signal for DPLL | 02 | r/w |

| 0: Reset asserted |

|

|

| 1: Normal operation |

|

|

Reference Clock Source Register

Table 30: Reference Clock Source Register

Bit | Description | Default | Access |

1..0 | Selects clock source for reference clock | 002 | r/w |

| 002: RCVD_CLK_0 |

|

|

| 012: RCVD_CLK_1 |

|

|

| 102: RCVD_CLK_2 |

|

|

| 112: RCVD_CLK_3 |

|

|

3..2 | Selects interrupt rate for interrupt | 002 | r/w |

| LCCB_INT_N clocked by 2 kHz system |

|

|

| clock reference |

|

|

002: 500 µs

012: 1 ms

102: 10 ms

112: 1 s

PENT/ATCA−717 | 145 |