Intelligent Platform Management Controller | Devices’ Features and Data Paths |

|

|

Intelligent Platform Management Controller

The blade provides an Intelligent Platform Management Controller (IPMC) unit based an the 8−bit Atmel ATmega AVR microcontrollers. The IPMC is fully compliant to the IPMI V1.5 standard and provides the following interfaces:aaa

SIPMB0A and IPMB0B available via the backplane

SIPMB−L connected to rear transition modulea

SI2C interfaces connected to on−board PMCs slots and sensors

SAnalog−to−Digital Conversion (ADC)interfaces connected to on−board sensors

SDigital I/O interfaces connected to on−board sensors

One of the main tasks of the IPMC is to control the power up and power down of the blade. For this purpose the IPMC is connected to the on−board power supply module via control and status lines. Various on−board IPMI sensors provide detailed information on the current power status of the blade to any interested party connected to the IPMI network.a

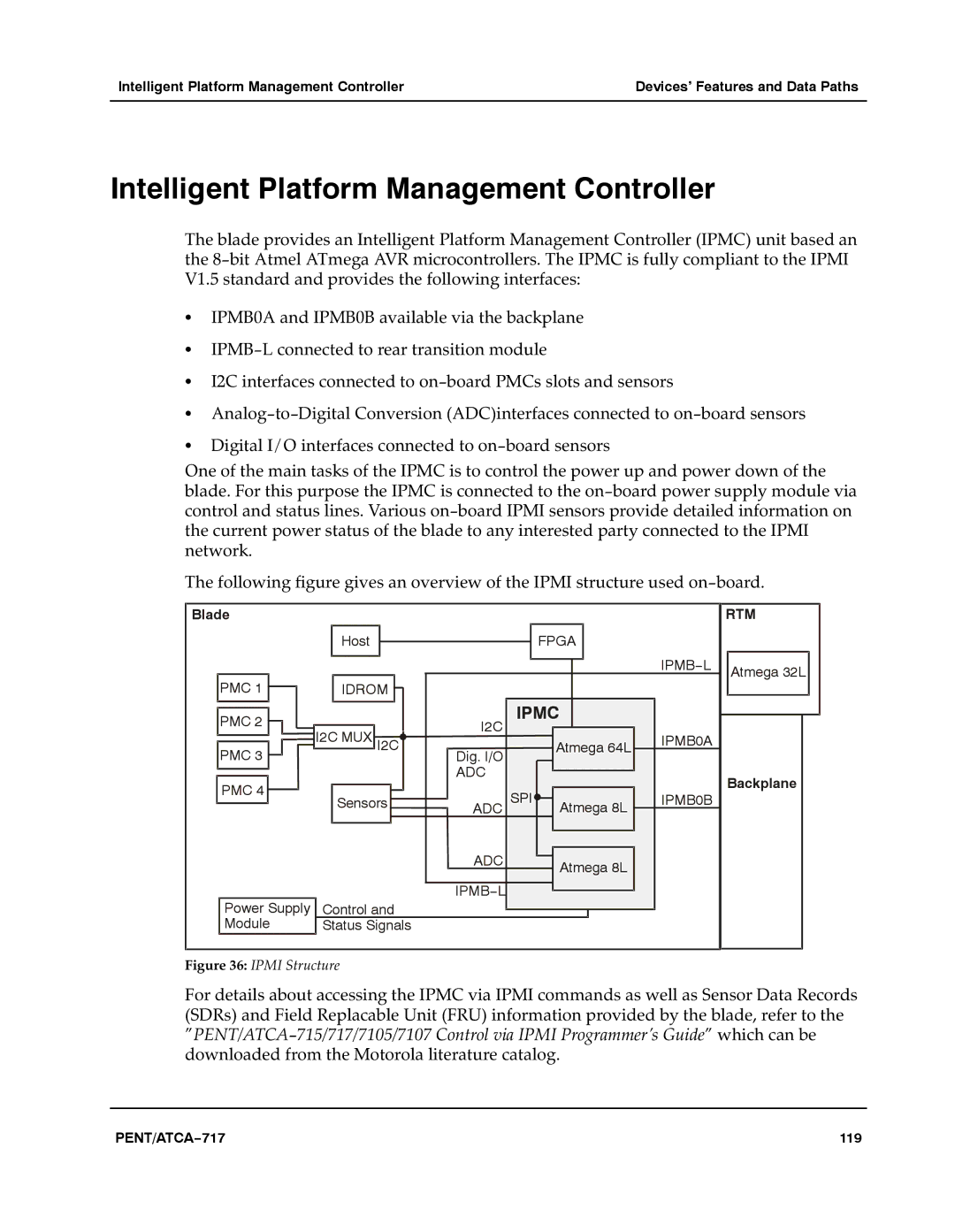

The following figure gives an overview of the IPMI structure used on−board.aaa

Blade

|

| Host | ||

PMC 1 |

| IDROM |

|

|

|

|

| ||

PMC 2 |

| I2C MUX I2C |

| |

PMC 3 |

|

| ||

| ||||

| ||||

|

|

|

| |

PMC 4 |

| Sensors | ||

|

| |||

Power Supply | Control and |

Module | Status Signals |

| RTM |

FPGA |

|

IPMB−L | Atmega 32L |

|

I2C | IPMC |

|

| IPMB0A | |||

Dig. I/O |

|

| Atmega 64L | ||||

|

|

|

| ||||

|

|

|

|

|

|

| |

ADC |

|

|

|

|

|

| Backplane |

| SPI |

|

|

|

|

| |

ADC |

|

| Atmega 8L |

| IPMB0B | ||

|

|

|

|

|

| ||

ADC | Atmega 8L |

| |

|

|

IPMB−L |

|

Figure 36: IPMI Structure

For details about accessing the IPMC via IPMI commands as well as Sensor Data Records (SDRs) and Field Replacable Unit (FRU) information provided by the blade, refer to the "PENT/ATCA−715/717/7105/7107 Control via IPMI Programmer’s Guide" which can be downloaded from the Motorola literature catalog.a

PENT/ATCA−717 | 119 |