BIOS | BIOS Post Codes |

|

|

BIOS Post Codes

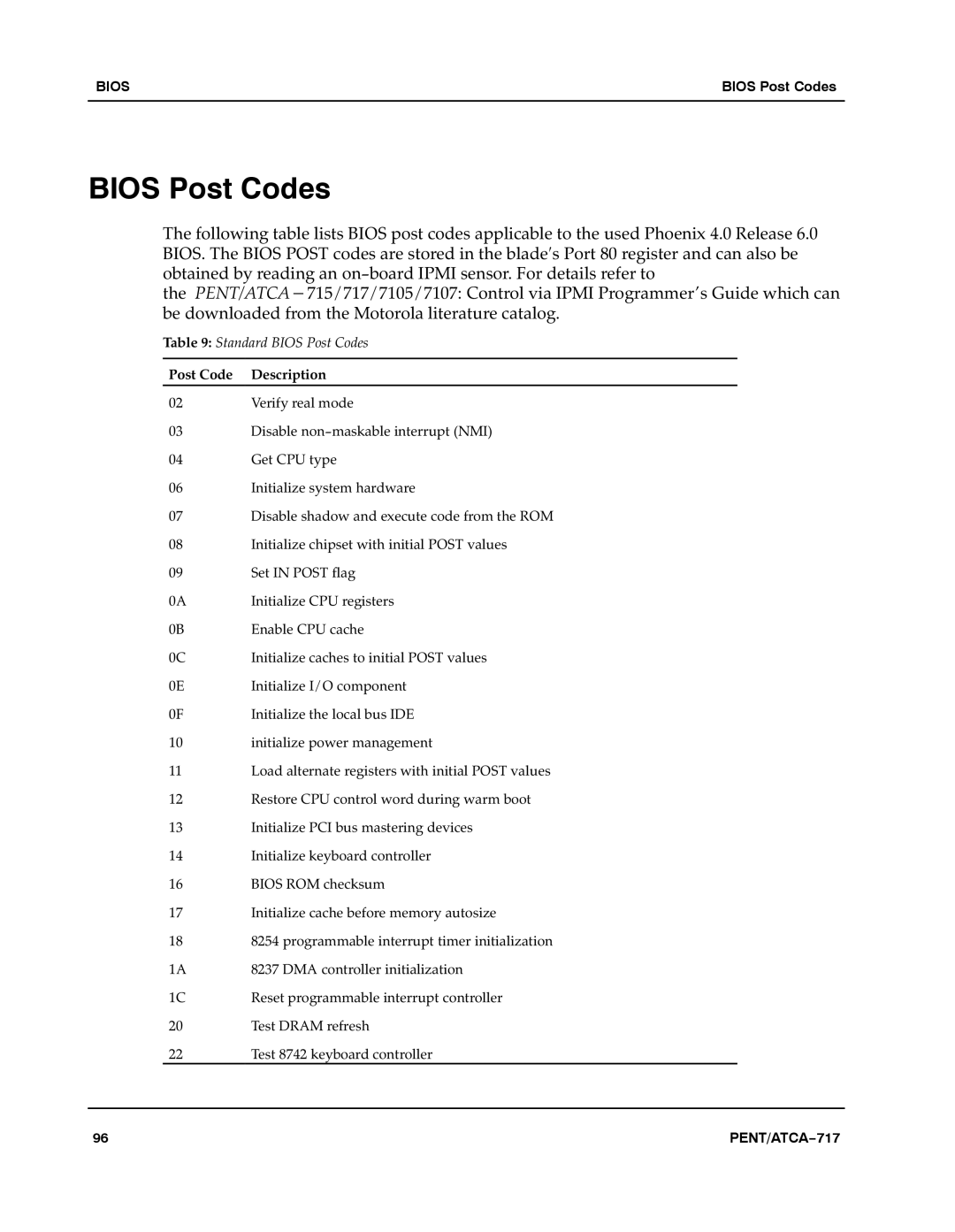

The following table lists BIOS post codes applicable to the used Phoenix 4.0 Release 6.0 BIOS. The BIOS POST codes are stored in the blade′s Port 80 register and can also be obtained by reading an on−board IPMI sensor. For details refer to theaPENT/ATCA*715/717/7105/7107: Control via IPMI Programmer’s Guide which can be downloaded from the Motorola literature catalog.aaa

Table 9: Standard BIOS Post Codes

Post Code | Description |

02 | Verify real mode |

03 | Disable non−maskable interrupt (NMI) |

04 | Get CPU type |

06 | Initialize system hardware |

07 | Disable shadow and execute code from the ROM |

08 | Initialize chipset with initial POST values |

09 | Set IN POST flag |

0A | Initialize CPU registers |

0B | Enable CPU cache |

0C | Initialize caches to initial POST values |

0E | Initialize I/O component |

0F | Initialize the local bus IDE |

10initialize power management

11Load alternate registers with initial POST values

12Restore CPU control word during warm boot

13Initialize PCI bus mastering devices

14Initialize keyboard controller

16BIOS ROM checksum

17Initialize cache before memory autosize

188254 programmable interrupt timer initialization

1A | 8237 DMA controller initialization |

1C | Reset programmable interrupt controller |

20 | Test DRAM refresh |

22 | Test 8742 keyboard controller |

96 | PENT/ATCA−717 |