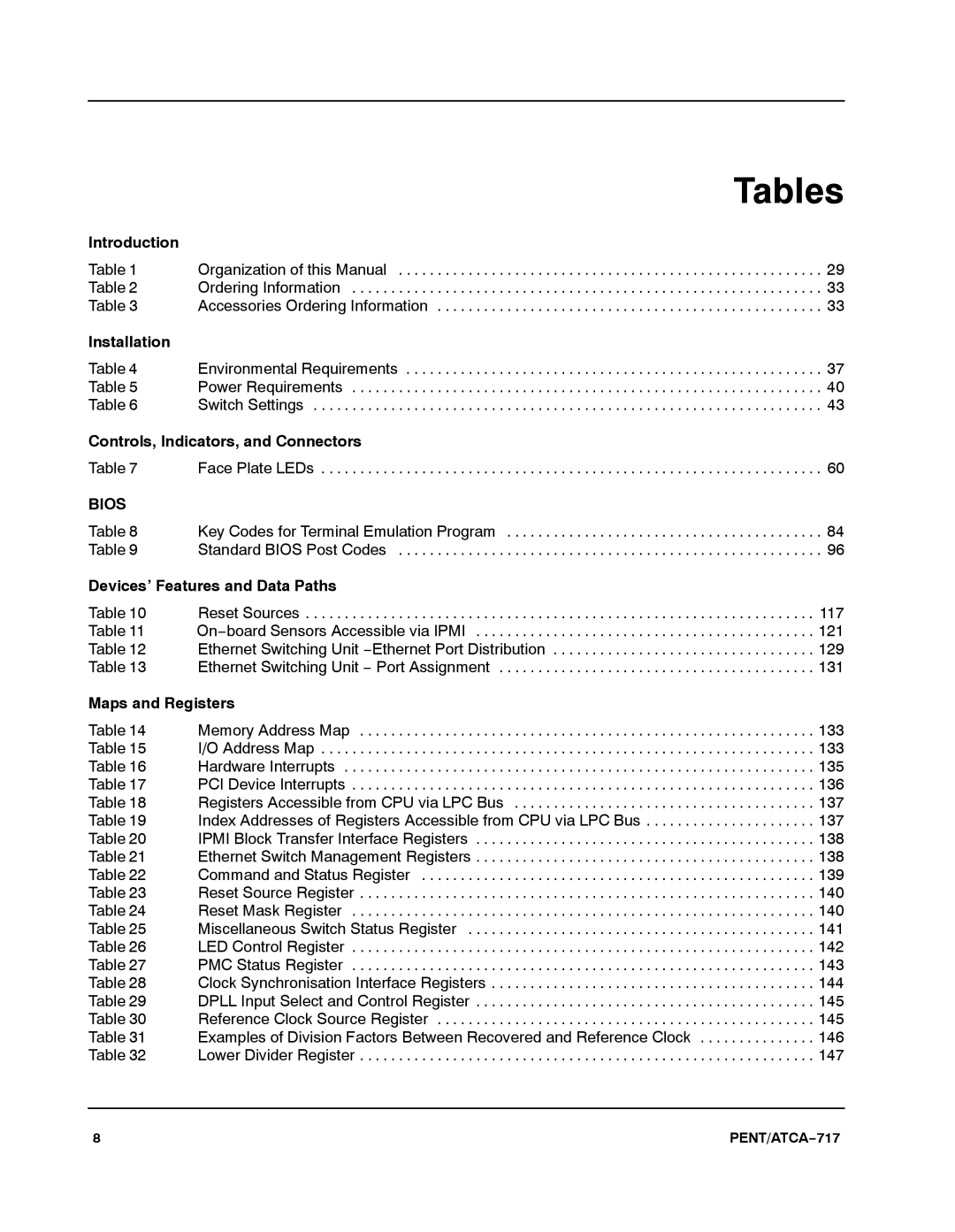

Tables

Introduction

Tablei1aaaaaaaOrganization of this Manual . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 Tablei2aaaaaaaOrdering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33 Tablei3aaaaaaaAccessories Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Installation

Tablei4aaaaaaaEnvironmental Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Tablei5aaaaaaaPower Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Tablei6aaaaaaaSwitch Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Controls, Indicators, and Connectors

Tablei7aaaaaaaFace Plate LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

BIOS

Tablei8aaaaaaaKey Codes for Terminal Emulation Program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84 Tablei9aaaaaaaStandard BIOS Post Codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Devices’ Features and Data Paths

Tablei10aaaaaaReset Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117 Tablei11aaaaaaOn−board Sensors Accessible via IPMI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121 Tablei12aaaaaaEthernet Switching Unit −Ethernet Port Distribution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129 Tablei13aaaaaaEthernet Switching Unit − Port Assignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

Maps and Registers

Tablei14aaaaaaMemory Address Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133 Tablei15aaaaaaI/O Address Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133 Tablei16aaaaaaHardware Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135 Tablei17aaaaaaPCI Device Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136 Tablei18aaaaaaRegisters Accessible from CPU via LPC Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137 Tablei19aaaaaaIndex Addresses of Registers Accessible from CPU via LPC Bus . . . . . . . . . . . . . . . . . . . . . . 137 Tablei20aaaaaaIPMI Block Transfer Interface Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138 Tablei21aaaaaaEthernet Switch Management Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138 Tablei22aaaaaaCommand and Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139 Tablei23aaaaaaReset Source Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140 Tablei24aaaaaaReset Mask Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140 Tablei25aaaaaaMiscellaneous Switch Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141 Tablei26aaaaaaLED Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142 Tablei27aaaaaaPMC Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143 Tablei28aaaaaaClock Synchronisation Interface Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144 Tablei29aaaaaaDPLL Input Select and Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145 Tablei30aaaaaaReference Clock Source Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145 Tablei31aaaaaaExamples of Division Factors Between Recovered and Reference Clock . . . . . . . . . . . . . . . 146 Tablei32aaaaaaLower Divider Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

8 | PENT/ATCA−717 |