Maps and Registers | PCI Devices |

|

|

PCI Devices

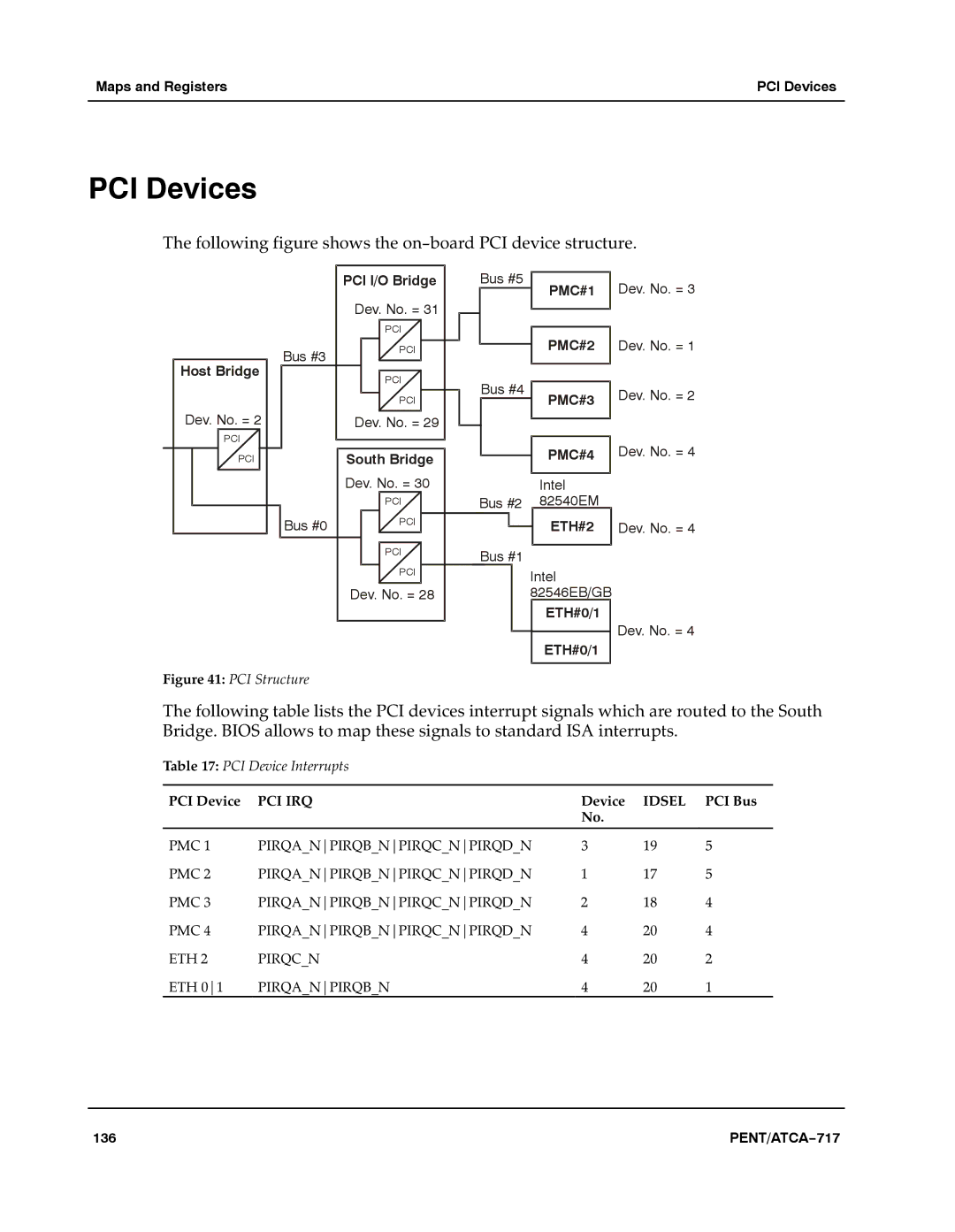

The following figure shows the on−board PCI device structure.aaa

PCI I/O Bridge | Bus #5 | PMC#1 | Dev. No. = 3 |

|

| ||

Dev. No. = 31 |

|

|

|

| PCI |

Bus #3 | PCI |

|

Host Bridge

PCI

PCI

| PMC#2 | Dev. No. = 1 |

Bus #4 | PMC#3 | Dev. No. = 2 |

| ||

|

|

Dev. No. = 2 |

| Dev. No. = 29 |

|

|

|

|

| ||

| PCI |

|

|

|

|

|

|

| Dev. No. = 4 |

| PCI |

| South Bridge |

|

| PMC#4 | |||

|

|

| |||||||

|

|

|

|

|

|

| |||

|

|

| Dev. No. = 30 |

|

| Intel |

| ||

|

|

| PCI |

| Bus #2 82540EM |

| |||

|

| Bus #0 | PCI |

|

|

| ETH#2 | Dev. No. = 4 | |

|

|

|

|

|

| ||||

|

|

| PCI | Bus #1 |

| ||||

|

|

|

|

|

| ||||

|

|

| PCI |

|

| Intel |

| ||

|

|

|

|

|

|

| |||

|

|

| Dev. No. = 28 |

| 82546EB/GB |

| |||

|

|

|

|

|

|

| ETH#0/1 |

| |

|

|

|

|

|

|

|

|

| Dev. No. = 4 |

|

|

|

|

|

|

| ETH#0/1 | ||

|

|

|

|

|

|

|

| ||

Figure 41: PCI Structure

The following table lists the PCI devices interrupt signals which are routed to the South Bridge. BIOS allows to map these signals to standard ISA interrupts.aaa

Table 17: PCI Device Interrupts

PCI Device | PCI IRQ | Device | IDSEL | PCI Bus |

|

| No. |

|

|

PMC 1 | PIRQA_NPIRQB_NPIRQC_NPIRQD_N | 3 | 19 | 5 |

PMC 2 | PIRQA_NPIRQB_NPIRQC_NPIRQD_N | 1 | 17 | 5 |

PMC 3 | PIRQA_NPIRQB_NPIRQC_NPIRQD_N | 2 | 18 | 4 |

PMC 4 | PIRQA_NPIRQB_NPIRQC_NPIRQD_N | 4 | 20 | 4 |

ETH 2 | PIRQC_N | 4 | 20 | 2 |

ETH 01 | PIRQA_NPIRQB_N | 4 | 20 | 1 |

136 | PENT/ATCA−717 |