|

|

|

|

|

|

|

|

|

| CY7C67300 | ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

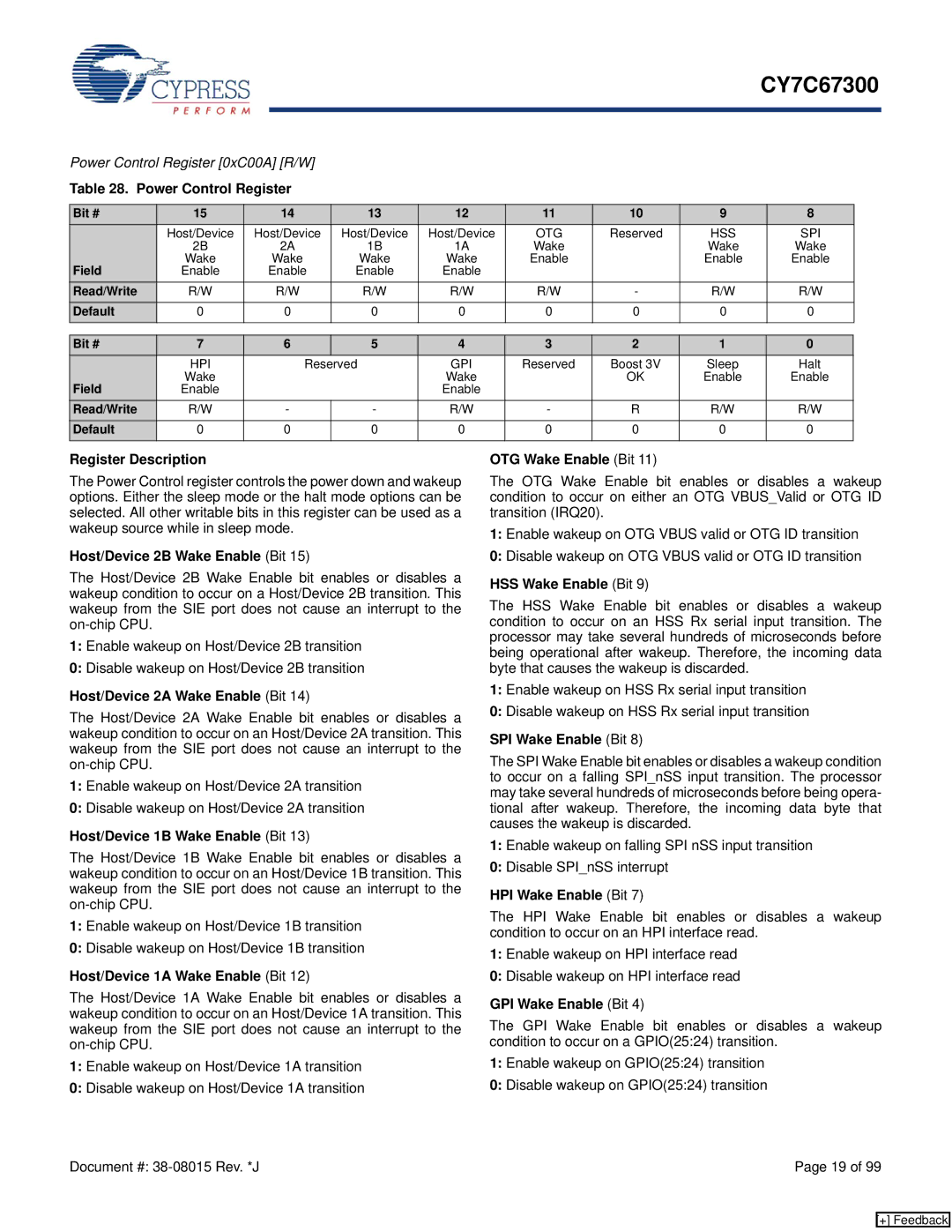

Power Control Register [0xC00A] [R/W] |

|

|

|

|

|

|

|

|

|

| ||||

Table 28. Power Control Register |

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

| ||

Bit # | 15 | 14 | 13 | 12 | 11 | 10 | 9 |

| 8 |

|

|

| ||

| Host/Device | Host/Device | Host/Device | Host/Device | OTG | Reserved | HSS |

| SPI |

|

| |||

| 2B |

|

| 2A | 1B | 1A | Wake |

| Wake |

| Wake |

| ||

Field | Wake |

|

| Wake | Wake | Wake | Enable |

| Enable |

| Enable |

| ||

Enable | Enable | Enable | Enable |

|

|

|

|

|

|

|

| |||

Read/Write | R/W |

|

| R/W | R/W | R/W | R/W | - | R/W |

| R/W |

|

| |

Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 |

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

| 0 |

|

|

| ||

| HPI |

|

| Reserved | GPI | Reserved | Boost 3V | Sleep |

| Halt |

| |||

Field | Wake |

|

|

|

| Wake |

| OK | Enable |

| Enable |

| ||

Enable |

|

|

|

| Enable |

|

|

|

|

|

|

|

| |

Read/Write | R/W | - | - | R/W | - | R | R/W |

| R/W |

|

|

| ||

Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 |

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Register Description

The Power Control register controls the power down and wakeup options. Either the sleep mode or the halt mode options can be selected. All other writable bits in this register can be used as a wakeup source while in sleep mode.

Host/Device 2B Wake Enable (Bit 15)

The Host/Device 2B Wake Enable bit enables or disables a wakeup condition to occur on a Host/Device 2B transition. This wakeup from the SIE port does not cause an interrupt to the

1:Enable wakeup on Host/Device 2B transition

0:Disable wakeup on Host/Device 2B transition

Host/Device 2A Wake Enable (Bit 14)

The Host/Device 2A Wake Enable bit enables or disables a wakeup condition to occur on an Host/Device 2A transition. This wakeup from the SIE port does not cause an interrupt to the

1:Enable wakeup on Host/Device 2A transition

0:Disable wakeup on Host/Device 2A transition

Host/Device 1B Wake Enable (Bit 13)

The Host/Device 1B Wake Enable bit enables or disables a wakeup condition to occur on an Host/Device 1B transition. This wakeup from the SIE port does not cause an interrupt to the

1:Enable wakeup on Host/Device 1B transition

0:Disable wakeup on Host/Device 1B transition

Host/Device 1A Wake Enable (Bit 12)

The Host/Device 1A Wake Enable bit enables or disables a wakeup condition to occur on an Host/Device 1A transition. This wakeup from the SIE port does not cause an interrupt to the

1:Enable wakeup on Host/Device 1A transition

0:Disable wakeup on Host/Device 1A transition

OTG Wake Enable (Bit 11)

The OTG Wake Enable bit enables or disables a wakeup condition to occur on either an OTG VBUS_Valid or OTG ID transition (IRQ20).

1:Enable wakeup on OTG VBUS valid or OTG ID transition

0:Disable wakeup on OTG VBUS valid or OTG ID transition

HSS Wake Enable (Bit 9)

The HSS Wake Enable bit enables or disables a wakeup condition to occur on an HSS Rx serial input transition. The processor may take several hundreds of microseconds before being operational after wakeup. Therefore, the incoming data byte that causes the wakeup is discarded.

1:Enable wakeup on HSS Rx serial input transition

0:Disable wakeup on HSS Rx serial input transition

SPI Wake Enable (Bit 8)

The SPI Wake Enable bit enables or disables a wakeup condition to occur on a falling SPI_nSS input transition. The processor may take several hundreds of microseconds before being opera- tional after wakeup. Therefore, the incoming data byte that causes the wakeup is discarded.

1:Enable wakeup on falling SPI nSS input transition

0:Disable SPI_nSS interrupt

HPI Wake Enable (Bit 7)

The HPI Wake Enable bit enables or disables a wakeup condition to occur on an HPI interface read.

1:Enable wakeup on HPI interface read

0:Disable wakeup on HPI interface read

GPI Wake Enable (Bit 4)

The GPI Wake Enable bit enables or disables a wakeup condition to occur on a GPIO(25:24) transition.

1:Enable wakeup on GPIO(25:24) transition

0:Disable wakeup on GPIO(25:24) transition

Document #: | Page 19 of 99 |

[+] Feedback