CY7C67300

Done1 Flag (Bit 2)

In host mode the Done 1 Flag bit is a read only bit that indicates if a host packet done interrupt occurs on Host 1. In device mode this read only bit indicates if an any of the endpoint interrupts occur on Device 1. Firmware needs to determine which endpoint interrupt occurred.

1:Interrupt triggered

0:Interrupt did not trigger

Reset1 Flag (Bit 1)

SPI Registers

The Reset1 Flag bit is a read only bit that indicates if a USB Reset interrupt occurs on either Host/Device 1.

1:Interrupt triggered

0:Interrupt did not trigger

Mailbox Out Flag (Bit 0)

The Mailbox Out Flag bit is a read only bit that indicates if a message is ready in the outgoing mailbox. This interrupt clears when the external host reads from the HPI Mailbox register.

1:Interrupt triggered

0:Interrupt did not trigger

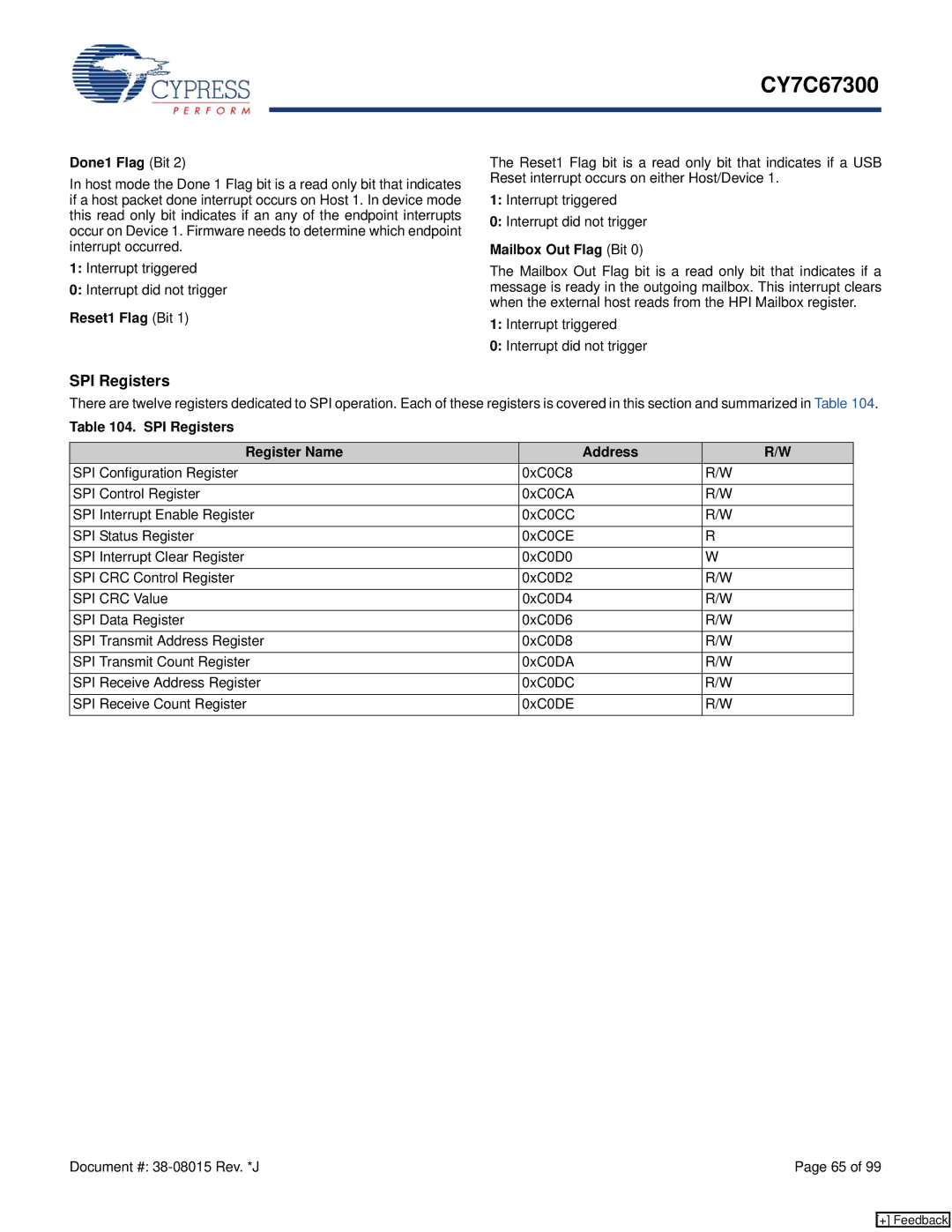

There are twelve registers dedicated to SPI operation. Each of these registers is covered in this section and summarized in Table 104.

Table 104. SPI Registers

Register Name | Address | R/W |

SPI Configuration Register | 0xC0C8 | R/W |

SPI Control Register | 0xC0CA | R/W |

SPI Interrupt Enable Register | 0xC0CC | R/W |

SPI Status Register | 0xC0CE | R |

SPI Interrupt Clear Register | 0xC0D0 | W |

SPI CRC Control Register | 0xC0D2 | R/W |

SPI CRC Value | 0xC0D4 | R/W |

SPI Data Register | 0xC0D6 | R/W |

SPI Transmit Address Register | 0xC0D8 | R/W |

SPI Transmit Count Register | 0xC0DA | R/W |

SPI Receive Address Register | 0xC0DC | R/W |

SPI Receive Count Register | 0xC0DE | R/W |

Document #: | Page 65 of 99 |

[+] Feedback