CY7C67300

Error, or OUT Exception Error. In addition, the NAK Interrupt Enable bit in the Device n Endpoint Control register can also be set so that NAK responses trigger this interrupt.

1:Enable EP1 Transaction Done interrupt

0:Disable EP1 Transaction Done interrupt

EP0 Interrupt Enable (Bit 0)

The EP0 Interrupt Enable bit enables or disables endpoint zero (EP0) Transaction Done interrupt. An EPx Transaction Done interrupt triggers when any of the following responses or events occur in a transaction for the device’s supplied Endpoint:

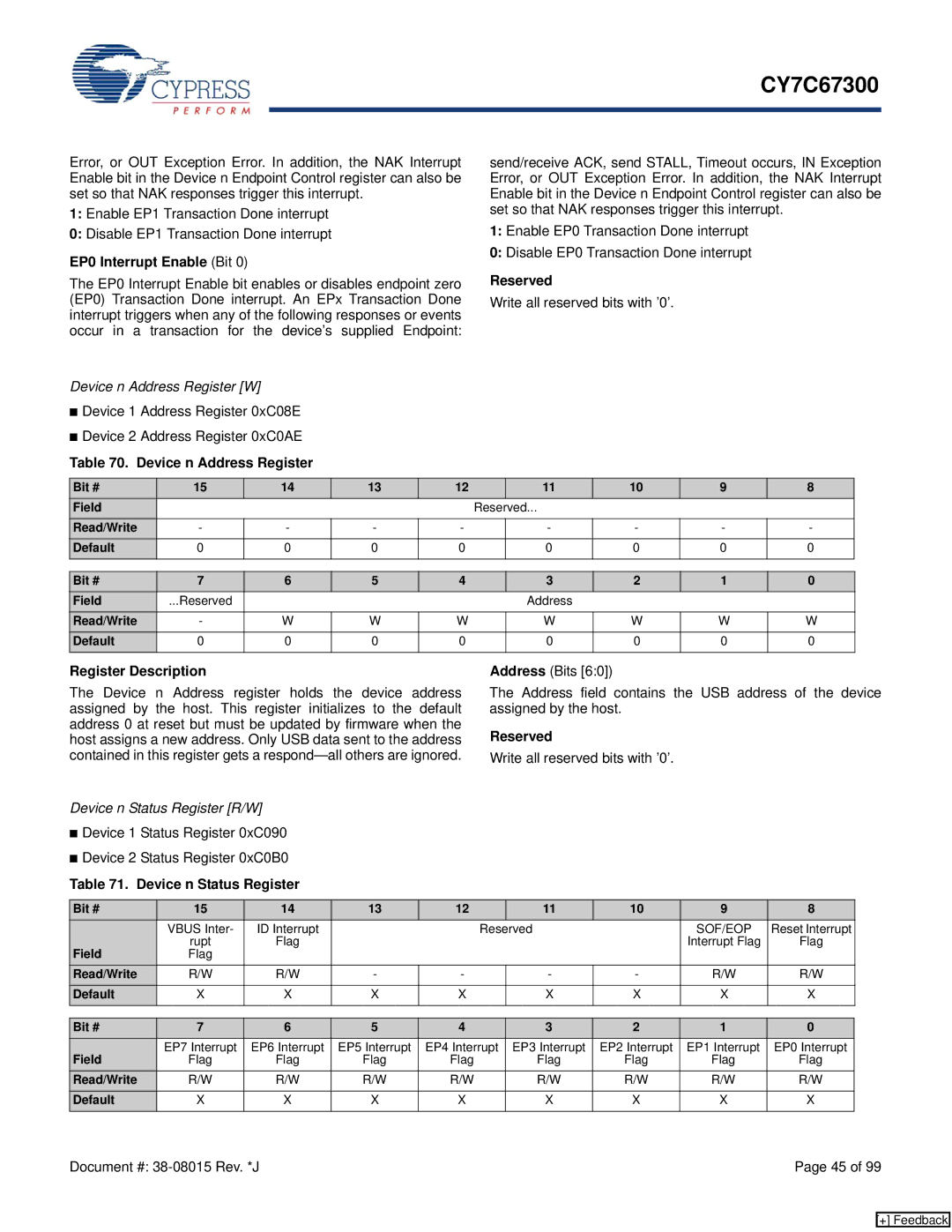

Device n Address Register [W]

■Device 1 Address Register 0xC08E

■Device 2 Address Register 0xC0AE

Table 70. Device n Address Register

send/receive ACK, send STALL, Timeout occurs, IN Exception Error, or OUT Exception Error. In addition, the NAK Interrupt Enable bit in the Device n Endpoint Control register can also be set so that NAK responses trigger this interrupt.

1:Enable EP0 Transaction Done interrupt

0:Disable EP0 Transaction Done interrupt

Reserved

Write all reserved bits with ’0’.

Bit # | 15 | 14 | 13 | 12 |

| 11 | 10 | 9 | 8 |

Field |

|

|

|

| Reserved... |

|

|

| |

Read/Write | - | - | - | - |

| - | - | - | - |

Default | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 |

|

|

|

|

|

|

|

|

|

|

Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

Field | ...Reserved |

|

|

| Address |

|

|

|

Read/Write | - | W | W | W | W | W | W | W |

Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|

|

|

|

|

|

|

|

|

Register Description

The Device n Address register holds the device address assigned by the host. This register initializes to the default address 0 at reset but must be updated by firmware when the host assigns a new address. Only USB data sent to the address contained in this register gets a

Device n Status Register [R/W]

■Device 1 Status Register 0xC090

■Device 2 Status Register 0xC0B0

Table 71. Device n Status Register

Address (Bits [6:0])

The Address field contains the USB address of the device assigned by the host.

Reserved

Write all reserved bits with ’0’.

Bit # | 15 | 14 | 13 | 12 |

| 11 | 10 | 9 | 8 |

| VBUS Inter- | ID Interrupt |

|

| Reserved |

| SOF/EOP | Reset Interrupt | |

Field | rupt | Flag |

|

|

|

|

| Interrupt Flag | Flag |

Flag |

|

|

|

|

|

|

|

| |

Read/Write | R/W | R/W | - | - |

| - | - | R/W | R/W |

Default | X | X | X | X |

| X | X | X | X |

|

|

|

|

|

|

|

|

|

|

Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

Field | EP7 Interrupt | EP6 Interrupt | EP5 Interrupt | EP4 Interrupt | EP3 Interrupt | EP2 Interrupt | EP1 Interrupt | EP0 Interrupt |

Flag | Flag | Flag | Flag | Flag | Flag | Flag | Flag | |

Read/Write | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

Default | X | X | X | X | X | X | X | X |

|

|

|

|

|

|

|

|

|

Document #: | Page 45 of 99 |

[+] Feedback