CY7C67300

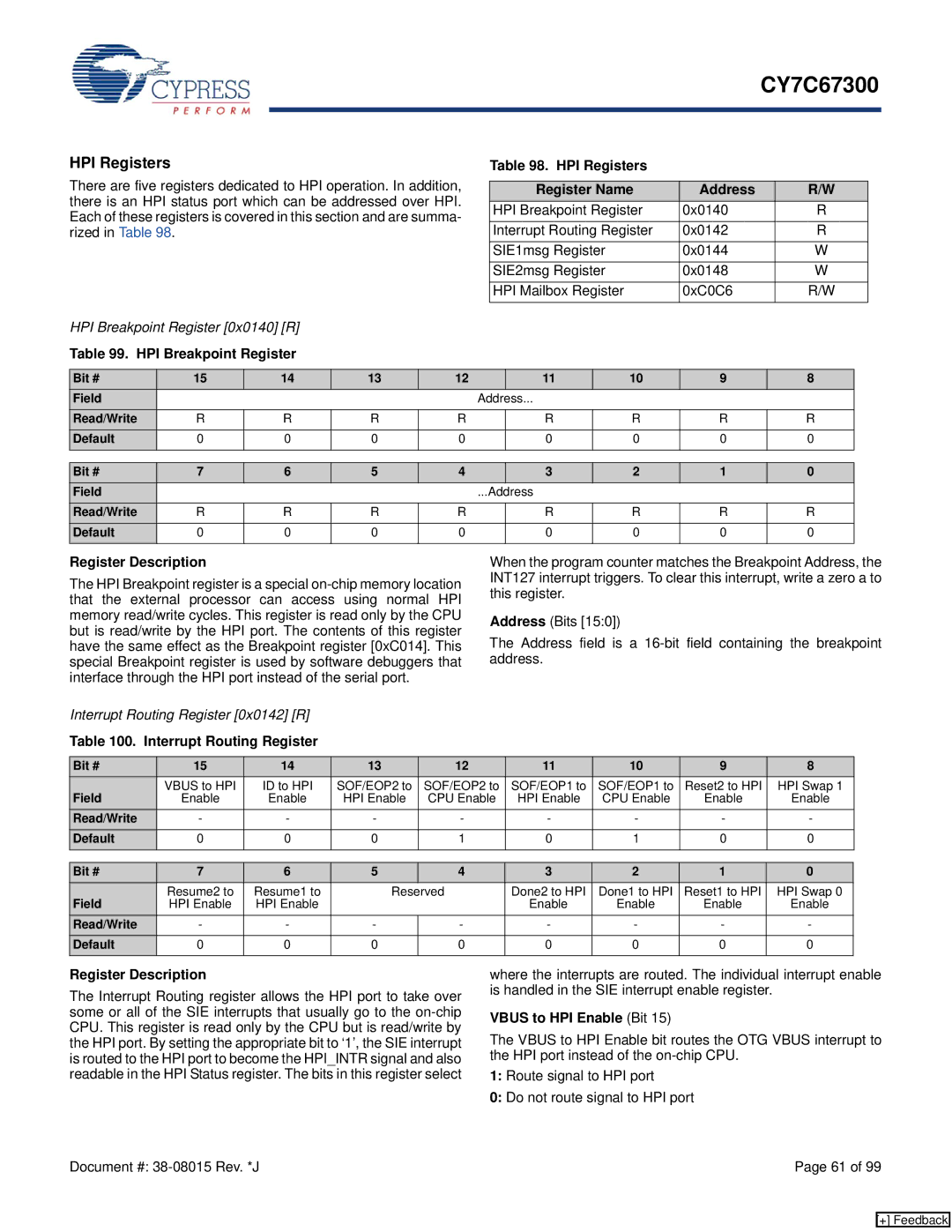

HPI Registers

There are five registers dedicated to HPI operation. In addition, there is an HPI status port which can be addressed over HPI. Each of these registers is covered in this section and are summa- rized in Table 98.

HPI Breakpoint Register [0x0140] [R]

Table 99. HPI Breakpoint Register

Table 98. HPI Registers

Register Name | Address | R/W |

HPI Breakpoint Register | 0x0140 | R |

Interrupt Routing Register | 0x0142 | R |

SIE1msg Register | 0x0144 | W |

SIE2msg Register | 0x0148 | W |

HPI Mailbox Register | 0xC0C6 | R/W |

Bit # | 15 | 14 | 13 | 12 |

| 11 | 10 | 9 | 8 |

Field |

|

|

|

| Address... |

|

|

| |

Read/Write | R | R | R | R |

| R | R | R | R |

Default | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 |

|

|

|

|

|

|

|

|

|

|

Bit # | 7 | 6 | 5 | 4 |

| 3 | 2 | 1 | 0 |

Field |

|

|

|

| ...Address |

|

|

| |

Read/Write | R | R | R | R |

| R | R | R | R |

Default | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 |

|

|

|

|

|

|

|

|

|

|

Register Description

The HPI Breakpoint register is a special

Interrupt Routing Register [0x0142] [R]

Table 100. Interrupt Routing Register

When the program counter matches the Breakpoint Address, the INT127 interrupt triggers. To clear this interrupt, write a zero a to this register.

Address (Bits [15:0])

The Address field is a

Bit # | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

Field | VBUS to HPI | ID to HPI | SOF/EOP2 to | SOF/EOP2 to | SOF/EOP1 to | SOF/EOP1 to | Reset2 to HPI | HPI Swap 1 |

Enable | Enable | HPI Enable | CPU Enable | HPI Enable | CPU Enable | Enable | Enable | |

Read/Write | - | - | - | - | - | - | - | - |

Default | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 |

|

|

|

|

|

|

|

|

|

Bit # | 7 | 6 | 5 |

| 4 | 3 | 2 | 1 | 0 |

Field | Resume2 to | Resume1 to |

| Reserved | Done2 to HPI | Done1 to HPI | Reset1 to HPI | HPI Swap 0 | |

HPI Enable | HPI Enable |

|

|

| Enable | Enable | Enable | Enable | |

Read/Write | - | - | - |

| - | - | - | - | - |

Default | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 |

|

|

|

|

|

|

|

|

|

|

Register Description

The Interrupt Routing register allows the HPI port to take over some or all of the SIE interrupts that usually go to the

where the interrupts are routed. The individual interrupt enable is handled in the SIE interrupt enable register.

VBUS to HPI Enable (Bit 15)

The VBUS to HPI Enable bit routes the OTG VBUS interrupt to the HPI port instead of the

1:Route signal to HPI port

0:Do not route signal to HPI port

Document #: | Page 61 of 99 |

[+] Feedback