CY7C67300

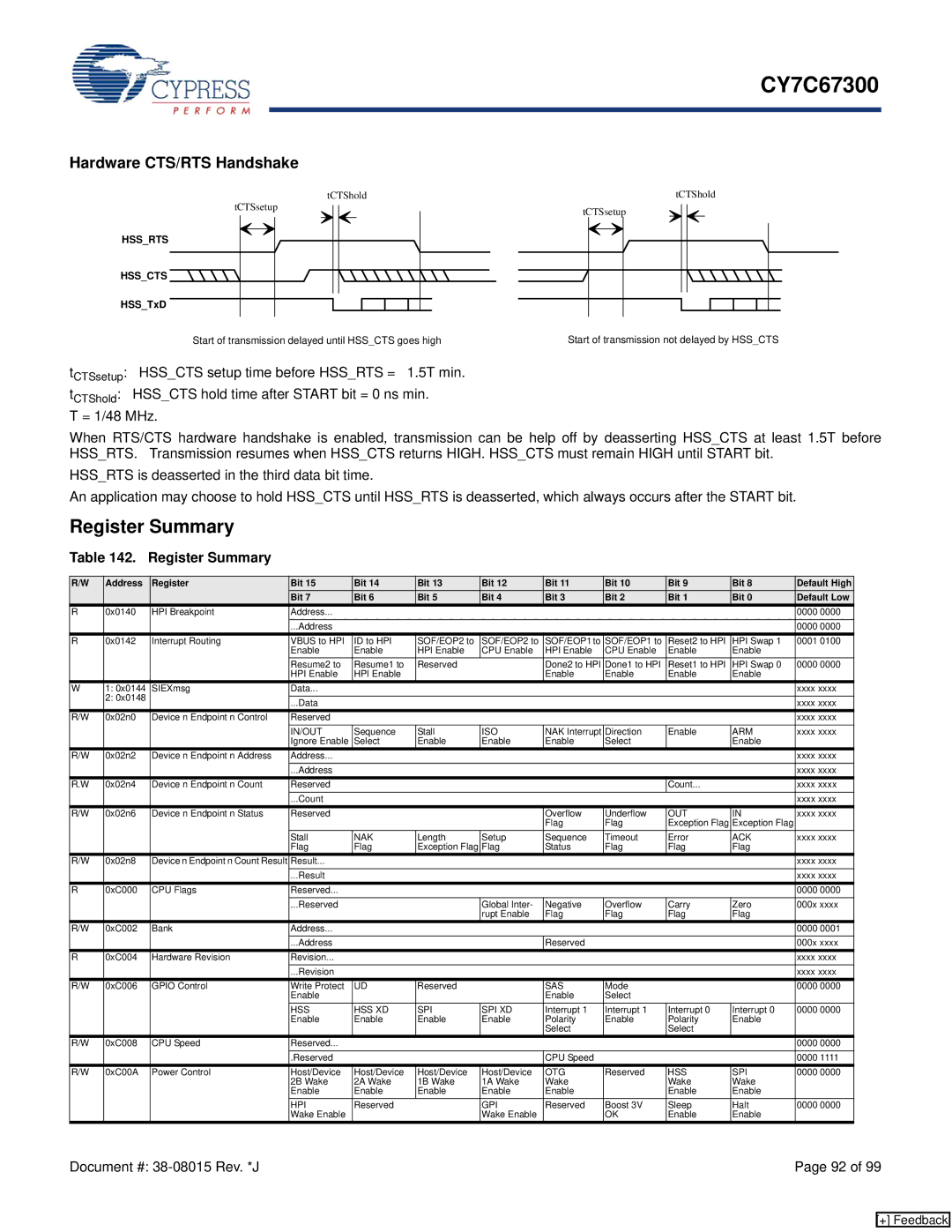

Hardware CTS/RTS Handshake

tCTShold

tCTSsetup

HSS_RTS

HSS_CTS

HSS_TxD

HSS_TxD

Start of transmission delayed until HSS_CTS goes high

tCTShold |

tCTSsetup |

Start of transmission not delayed by HSS_CTS

tCTSsetup: HSS_CTS setup time before HSS_RTS = 1.5T min.

tCTShold: HSS_CTS hold time after START bit = 0 ns min. T = 1/48 MHz.

When RTS/CTS hardware handshake is enabled, transmission can be help off by deasserting HSS_CTS at least 1.5T before HSS_RTS. Transmission resumes when HSS_CTS returns HIGH. HSS_CTS must remain HIGH until START bit.

HSS_RTS is deasserted in the third data bit time.

An application may choose to hold HSS_CTS until HSS_RTS is deasserted, which always occurs after the START bit.

Register Summary

Table 142. | Register Summary |

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

R/W | Address | Register | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Default High |

|

|

|

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Default Low |

|

R | 0x0140 | HPI Breakpoint | Address... |

|

|

|

|

|

|

| 0000 0000 |

|

|

|

| ...Address |

|

|

|

|

|

|

| 0000 0000 |

|

R | 0x0142 | Interrupt Routing | VBUS to HPI | ID to HPI | SOF/EOP2 to | SOF/EOP2 to | SOF/EOP1 to | SOF/EOP1 to | Reset2 to HPI | HPI Swap 1 | 0001 0100 |

|

|

|

| Enable | Enable | HPI Enable | CPU Enable | HPI Enable | CPU Enable | Enable | Enable |

|

|

|

|

| Resume2 to | Resume1 to | Reserved |

| Done2 to HPI | Done1 to HPI | Reset1 to HPI | HPI Swap 0 | 0000 0000 |

|

|

|

| HPI Enable | HPI Enable |

|

| Enable | Enable | Enable | Enable |

|

|

W | 1: 0x0144 | SIEXmsg | Data... |

|

|

|

|

|

|

| xxxx xxxx |

|

| 2: 0x0148 |

|

|

|

|

|

|

|

|

|

|

|

|

| ...Data |

|

|

|

|

|

|

| xxxx xxxx |

| |

|

|

|

|

|

|

|

|

|

|

| ||

R/W | 0x02n0 | Device n Endpoint n Control | Reserved |

|

|

|

|

|

|

| xxxx xxxx |

|

|

|

| IN/OUT | Sequence | Stall | ISO | NAK Interrupt | Direction | Enable | ARM | xxxx xxxx |

|

|

|

| Ignore Enable | Select | Enable | Enable | Enable | Select |

| Enable |

|

|

R/W | 0x02n2 | Device n Endpoint n Address | Address... |

|

|

|

|

|

|

| xxxx xxxx |

|

|

|

| ...Address |

|

|

|

|

|

|

| xxxx xxxx |

|

R.W | 0x02n4 | Device n Endpoint n Count | Reserved |

|

|

|

|

| Count... |

| xxxx xxxx |

|

|

|

| ...Count |

|

|

|

|

|

|

| xxxx xxxx |

|

R/W | 0x02n6 | Device n Endpoint n Status | Reserved |

|

|

| Overflow | Underflow | OUT | IN | xxxx xxxx |

|

|

|

|

|

|

|

| Flag | Flag | Exception Flag | Exception Flag |

|

|

|

|

| Stall | NAK | Length | Setup | Sequence | Timeout | Error | ACK | xxxx xxxx |

|

|

|

| Flag | Flag | Exception Flag | Flag | Status | Flag | Flag | Flag |

|

|

R/W | 0x02n8 | Device n Endpoint n Count Result | Result... |

|

|

|

|

|

|

| xxxx xxxx |

|

|

|

| ...Result |

|

|

|

|

|

|

| xxxx xxxx |

|

R | 0xC000 | CPU Flags | Reserved... |

|

|

|

|

|

|

| 0000 0000 |

|

|

|

| ...Reserved |

|

| Global Inter- | Negative | Overflow | Carry | Zero | 000x xxxx |

|

|

|

|

|

|

| rupt Enable | Flag | Flag | Flag | Flag |

|

|

R/W | 0xC002 | Bank | Address... |

|

|

|

|

|

|

| 0000 0001 |

|

|

|

| ...Address |

|

|

| Reserved |

|

|

| 000x xxxx |

|

R | 0xC004 | Hardware Revision | Revision... |

|

|

|

|

|

|

| xxxx xxxx |

|

|

|

| ...Revision |

|

|

|

|

|

|

| xxxx xxxx |

|

R/W | 0xC006 | GPIO Control | Write Protect | UD | Reserved |

| SAS | Mode |

|

| 0000 0000 |

|

|

|

| Enable |

|

|

| Enable | Select |

|

|

|

|

|

|

| HSS | HSS XD | SPI | SPI XD | Interrupt 1 | Interrupt 1 | Interrupt 0 | Interrupt 0 | 0000 0000 |

|

|

|

| Enable | Enable | Enable | Enable | Polarity | Enable | Polarity | Enable |

|

|

|

|

|

|

|

|

| Select |

| Select |

|

|

|

R/W | 0xC008 | CPU Speed | Reserved... |

|

|

|

|

|

|

| 0000 0000 |

|

|

|

| .Reserved |

|

|

| CPU Speed |

|

|

| 0000 1111 |

|

R/W | 0xC00A | Power Control | Host/Device | Host/Device | Host/Device | Host/Device | OTG | Reserved | HSS | SPI | 0000 0000 |

|

|

|

| 2B Wake | 2A Wake | 1B Wake | 1A Wake | Wake |

| Wake | Wake |

|

|

|

|

| Enable | Enable | Enable | Enable | Enable |

| Enable | Enable |

|

|

|

|

| HPI | Reserved |

| GPI | Reserved | Boost 3V | Sleep | Halt | 0000 0000 |

|

|

|

| Wake Enable |

|

| Wake Enable |

| OK | Enable | Enable |

|

|

Document #: |

|

|

|

|

|

|

|

| Page 92 of 99 | |||

[+] Feedback