CY7C67300

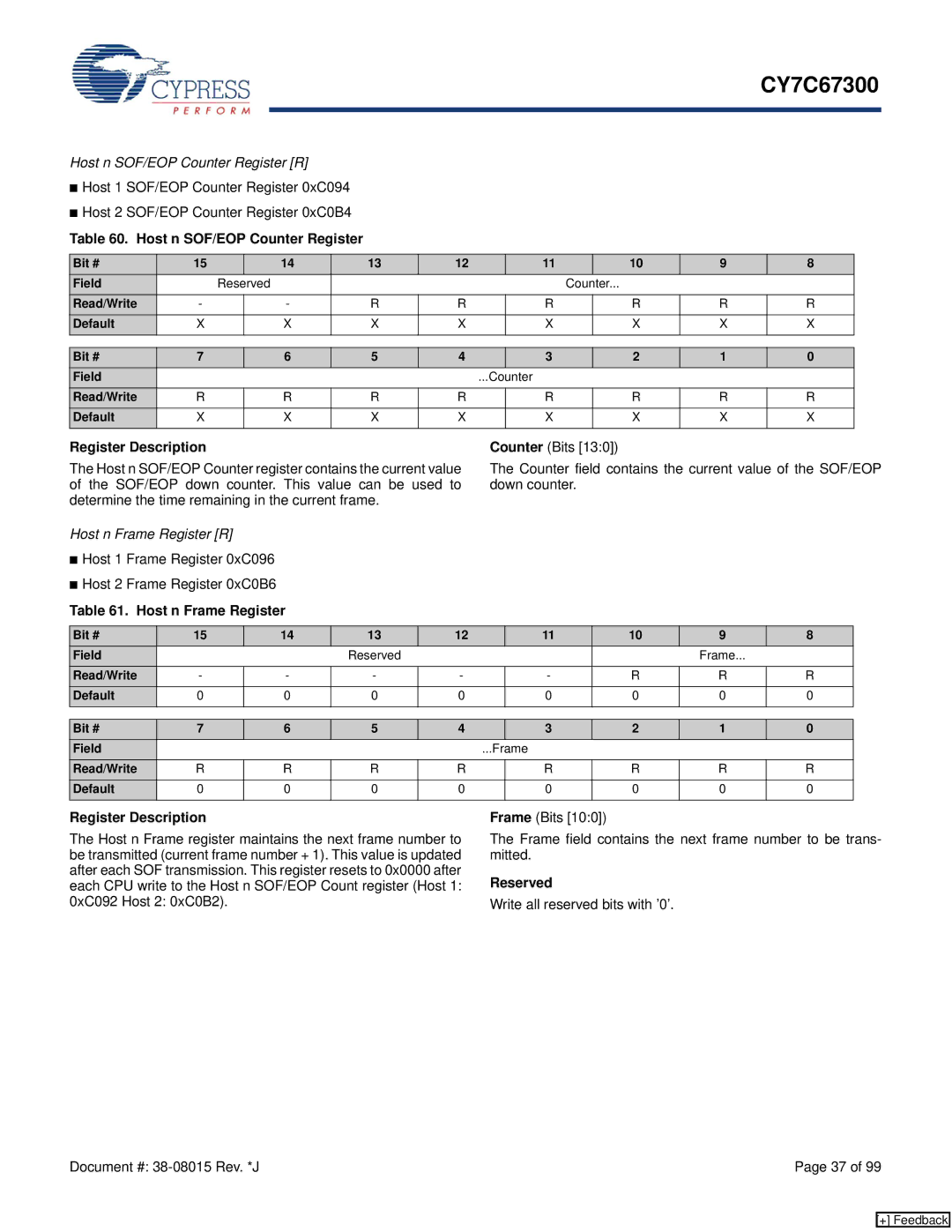

Host n SOF/EOP Counter Register [R]

■Host 1 SOF/EOP Counter Register 0xC094

■Host 2 SOF/EOP Counter Register 0xC0B4

Table 60. Host n SOF/EOP Counter Register

Bit # | 15 |

| 14 | 13 | 12 | 11 |

| 10 | 9 | 8 |

Field | Reserved |

|

|

|

| Counter... |

|

| ||

Read/Write | - |

| - | R | R | R |

| R | R | R |

Default | X |

| X | X | X | X |

| X | X | X |

|

|

|

|

|

|

|

|

|

|

|

Bit # | 7 | 6 | 5 | 4 |

| 3 | 2 | 1 | 0 |

Field |

|

|

|

| ...Counter |

|

|

| |

Read/Write | R | R | R | R |

| R | R | R | R |

Default | X | X | X | X |

| X | X | X | X |

|

|

|

|

|

|

|

|

|

|

Register Description

The Host n SOF/EOP Counter register contains the current value of the SOF/EOP down counter. This value can be used to determine the time remaining in the current frame.

Host n Frame Register [R]

■Host 1 Frame Register 0xC096

■Host 2 Frame Register 0xC0B6

Table 61. Host n Frame Register

Counter (Bits [13:0])

The Counter field contains the current value of the SOF/EOP down counter.

Bit # | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

Field |

|

| Reserved |

|

|

| Frame... |

|

Read/Write | - | - | - | - | - | R | R | R |

Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|

|

|

|

|

|

|

|

|

Bit # | 7 | 6 | 5 | 4 |

| 3 | 2 | 1 | 0 |

Field |

|

|

|

| ...Frame |

|

|

| |

Read/Write | R | R | R | R |

| R | R | R | R |

Default | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 |

|

|

|

|

|

|

|

|

|

|

Register Description

The Host n Frame register maintains the next frame number to be transmitted (current frame number + 1). This value is updated after each SOF transmission. This register resets to 0x0000 after each CPU write to the Host n SOF/EOP Count register (Host 1: 0xC092 Host 2: 0xC0B2).

Frame (Bits [10:0])

The Frame field contains the next frame number to be trans- mitted.

Reserved

Write all reserved bits with ’0’.

Document #: | Page 37 of 99 |

[+] Feedback