CY7C67300

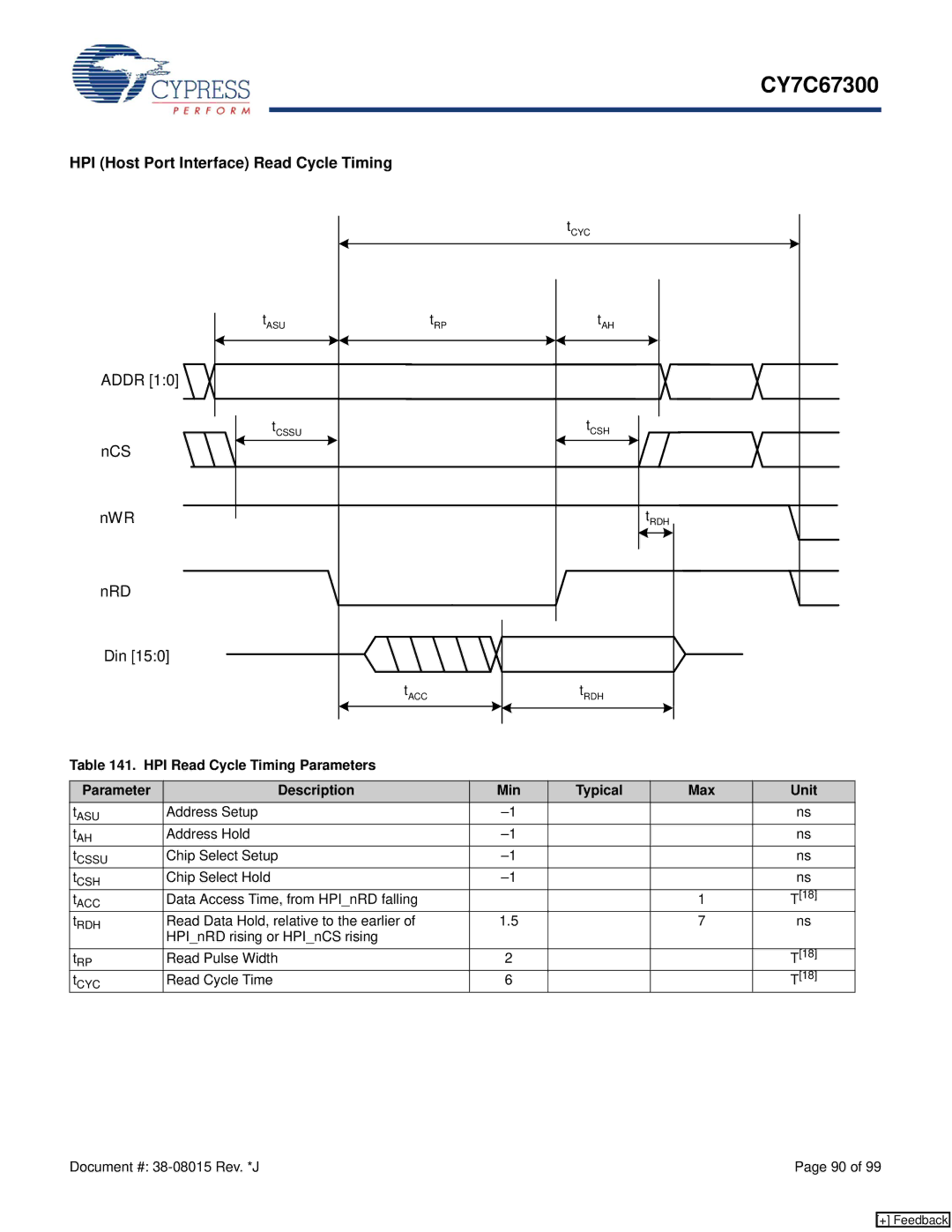

HPI (Host Port Interface) Read Cycle Timing

|

| tCYC |

tASU | tRP | tAH |

ADDR [1:0] |

|

|

tCSSU |

| tCSH |

nCS |

|

|

nWR |

| tRDH |

nRD |

|

|

Din [15:0] |

|

|

| tACC | tRDH |

Table 141. HPI Read Cycle Timing Parameters

Parameter | Description | Min | Typical | Max | Unit |

tASU | Address Setup |

|

| ns | |

tAH | Address Hold |

|

| ns | |

tCSSU | Chip Select Setup |

|

| ns | |

tCSH | Chip Select Hold |

|

| ns | |

t | Data Access Time, from HPI_nRD falling |

|

| 1 | T[18] |

ACC |

|

|

|

|

|

tRDH | Read Data Hold, relative to the earlier of | 1.5 |

| 7 | ns |

| HPI_nRD rising or HPI_nCS rising |

|

|

|

|

tRP | Read Pulse Width | 2 |

|

| T[18] |

tCYC | Read Cycle Time | 6 |

|

| T[18] |

Document #: | Page 90 of 99 |

[+] Feedback