|

|

|

|

|

|

|

|

|

| CY7C67300 | |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

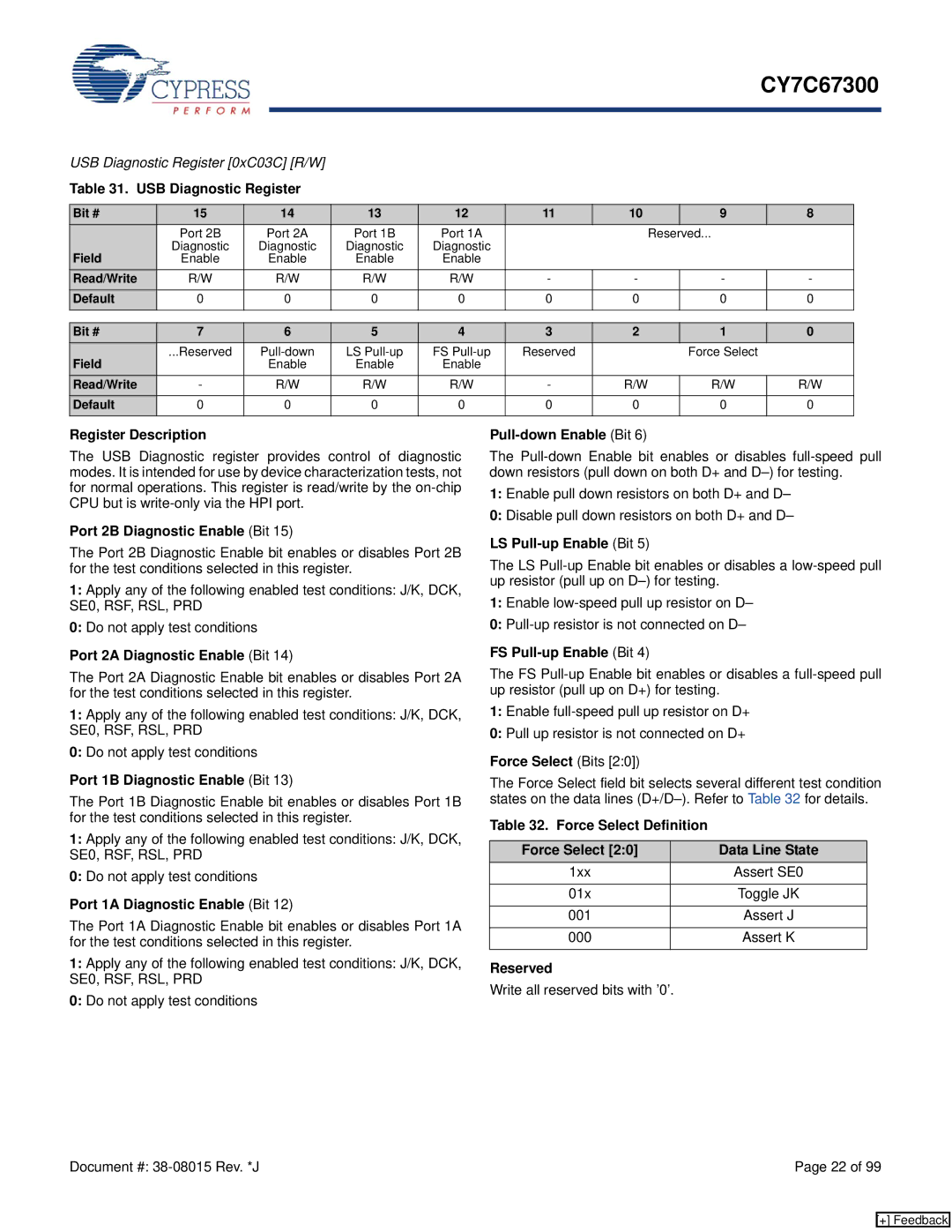

USB Diagnostic Register [0xC03C] [R/W] |

|

|

|

|

|

|

|

|

| ||||

Table 31. USB Diagnostic Register |

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

| ||

Bit # | 15 | 14 | 13 | 12 | 11 | 10 | 9 |

| 8 |

|

| ||

| Port 2B | Port 2A | Port 1B | Port 1A |

| Reserved... |

|

|

|

| |||

Field | Diagnostic | Diagnostic | Diagnostic | Diagnostic |

|

|

|

|

|

|

| ||

Enable | Enable | Enable | Enable |

|

|

|

|

|

|

| |||

Read/Write | R/W |

|

| R/W | R/W | R/W | - | - | - |

| - |

|

|

Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 |

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

| 0 |

|

| ||

Field | ...Reserved | LS | FS | Reserved |

| Force Select |

|

|

|

| |||

| Enable | Enable | Enable |

|

|

|

|

|

|

| |||

Read/Write | - |

|

| R/W | R/W | R/W | - | R/W | R/W |

| R/W |

|

|

Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 |

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Register Description

The USB Diagnostic register provides control of diagnostic modes. It is intended for use by device characterization tests, not for normal operations. This register is read/write by the

Port 2B Diagnostic Enable (Bit 15)

The Port 2B Diagnostic Enable bit enables or disables Port 2B for the test conditions selected in this register.

1:Apply any of the following enabled test conditions: J/K, DCK, SE0, RSF, RSL, PRD

0:Do not apply test conditions

Port 2A Diagnostic Enable (Bit 14)

The Port 2A Diagnostic Enable bit enables or disables Port 2A for the test conditions selected in this register.

1:Apply any of the following enabled test conditions: J/K, DCK, SE0, RSF, RSL, PRD

0:Do not apply test conditions

Port 1B Diagnostic Enable (Bit 13)

The Port 1B Diagnostic Enable bit enables or disables Port 1B for the test conditions selected in this register.

1:Apply any of the following enabled test conditions: J/K, DCK, SE0, RSF, RSL, PRD

0:Do not apply test conditions

Port 1A Diagnostic Enable (Bit 12)

The Port 1A Diagnostic Enable bit enables or disables Port 1A for the test conditions selected in this register.

1:Apply any of the following enabled test conditions: J/K, DCK, SE0, RSF, RSL, PRD

0:Do not apply test conditions

Pull-down Enable (Bit 6)

The

1:Enable pull down resistors on both D+ and D–

0:Disable pull down resistors on both D+ and D–

LS Pull-up Enable (Bit 5)

The LS

1:Enable

0:

FS Pull-up Enable (Bit 4)

The FS

1:Enable

0:Pull up resistor is not connected on D+

Force Select (Bits [2:0])

The Force Select field bit selects several different test condition states on the data lines

Table 32. Force Select Definition

Force Select [2:0] |

| Data Line State |

1xx |

| Assert SE0 |

|

|

|

01x |

| Toggle JK |

|

|

|

001 |

| Assert J |

|

|

|

000 |

| Assert K |

|

|

|

Reserved |

| |

Write all reserved bits with ’0’. |

| |

Document #: | Page 22 of 99 |

[+] Feedback