CY7C67300

USB Device Only Registers

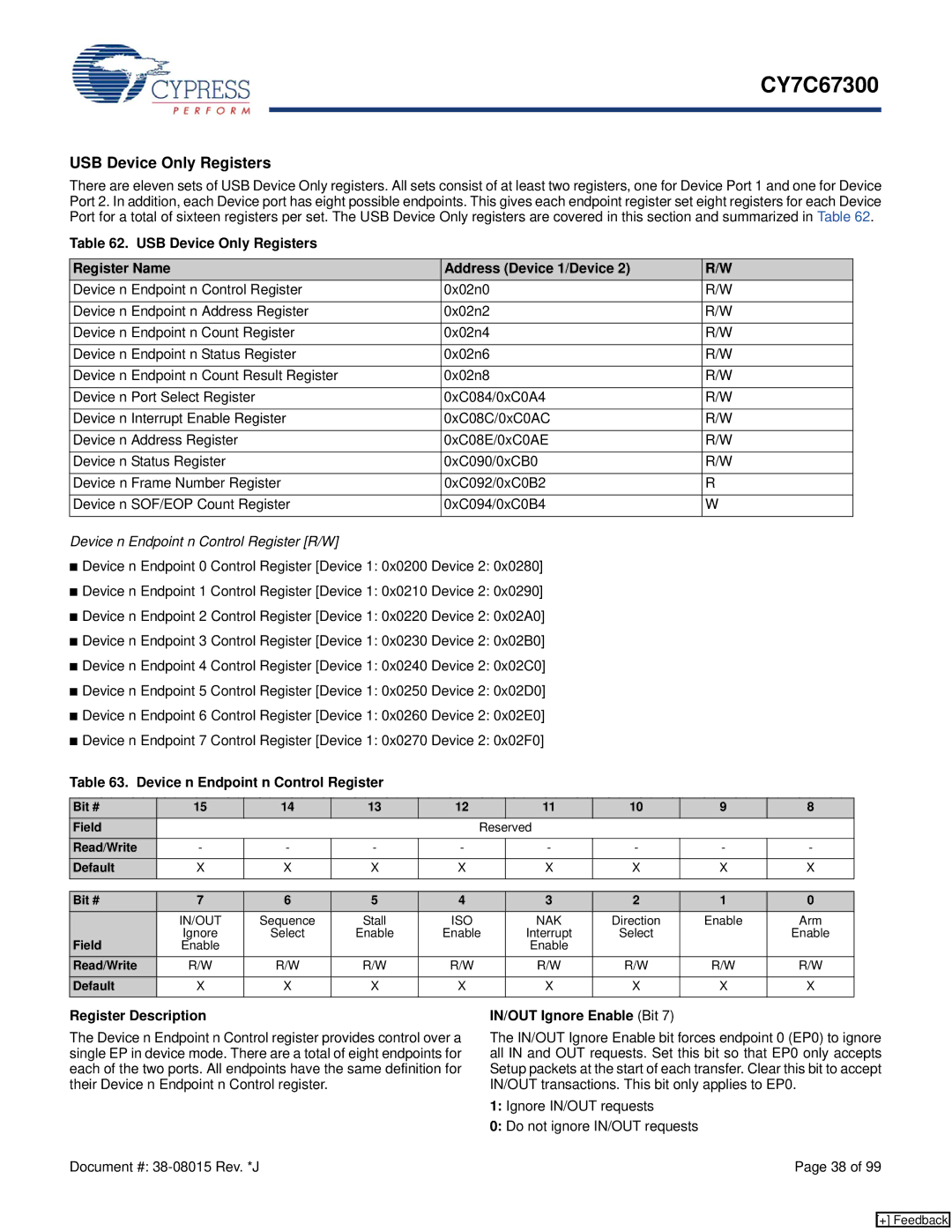

There are eleven sets of USB Device Only registers. All sets consist of at least two registers, one for Device Port 1 and one for Device Port 2. In addition, each Device port has eight possible endpoints. This gives each endpoint register set eight registers for each Device Port for a total of sixteen registers per set. The USB Device Only registers are covered in this section and summarized in Table 62.

Table 62. USB Device Only Registers

Register Name | Address (Device 1/Device 2) | R/W |

Device n Endpoint n Control Register | 0x02n0 | R/W |

Device n Endpoint n Address Register | 0x02n2 | R/W |

|

|

|

Device n Endpoint n Count Register | 0x02n4 | R/W |

|

|

|

Device n Endpoint n Status Register | 0x02n6 | R/W |

|

|

|

Device n Endpoint n Count Result Register | 0x02n8 | R/W |

|

|

|

Device n Port Select Register | 0xC084/0xC0A4 | R/W |

Device n Interrupt Enable Register | 0xC08C/0xC0AC | R/W |

|

|

|

Device n Address Register | 0xC08E/0xC0AE | R/W |

|

|

|

Device n Status Register | 0xC090/0xCB0 | R/W |

|

|

|

Device n Frame Number Register | 0xC092/0xC0B2 | R |

|

|

|

Device n SOF/EOP Count Register | 0xC094/0xC0B4 | W |

Device n Endpoint n Control Register [R/W]

■Device n Endpoint 0 Control Register [Device 1: 0x0200 Device 2: 0x0280]

■Device n Endpoint 1 Control Register [Device 1: 0x0210 Device 2: 0x0290]

■Device n Endpoint 2 Control Register [Device 1: 0x0220 Device 2: 0x02A0]

■Device n Endpoint 3 Control Register [Device 1: 0x0230 Device 2: 0x02B0]

■Device n Endpoint 4 Control Register [Device 1: 0x0240 Device 2: 0x02C0]

■Device n Endpoint 5 Control Register [Device 1: 0x0250 Device 2: 0x02D0]

■Device n Endpoint 6 Control Register [Device 1: 0x0260 Device 2: 0x02E0]

■Device n Endpoint 7 Control Register [Device 1: 0x0270 Device 2: 0x02F0]

Table 63. Device n Endpoint n Control Register

Bit # | 15 | 14 | 13 | 12 |

| 11 | 10 | 9 | 8 |

Field |

|

|

|

| Reserved |

|

|

| |

Read/Write | - | - | - | - |

| - | - | - | - |

Default | X | X | X | X |

| X | X | X | X |

|

|

|

|

|

|

|

|

|

|

Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| IN/OUT | Sequence | Stall | ISO | NAK | Direction | Enable | Arm |

Field | Ignore | Select | Enable | Enable | Interrupt | Select |

| Enable |

Enable |

|

|

| Enable |

|

|

| |

Read/Write | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

Default | X | X | X | X | X | X | X | X |

|

|

|

|

|

|

|

|

|

Register Description

The Device n Endpoint n Control register provides control over a single EP in device mode. There are a total of eight endpoints for each of the two ports. All endpoints have the same definition for their Device n Endpoint n Control register.

IN/OUT Ignore Enable (Bit 7)

The IN/OUT Ignore Enable bit forces endpoint 0 (EP0) to ignore all IN and OUT requests. Set this bit so that EP0 only accepts Setup packets at the start of each transfer. Clear this bit to accept IN/OUT transactions. This bit only applies to EP0.

1:Ignore IN/OUT requests

0:Do not ignore IN/OUT requests

Document #: | Page 38 of 99 |

[+] Feedback