CY7C67300

Register Description | Address (Bits [15:0]) |

The Device n Endpoint n Address register is used as the base pointer into memory space for the current Endpoint transaction. There are a total of eight endpoints for each of the two ports. All endpoints have the same definition for their Device n Endpoint n Address register.

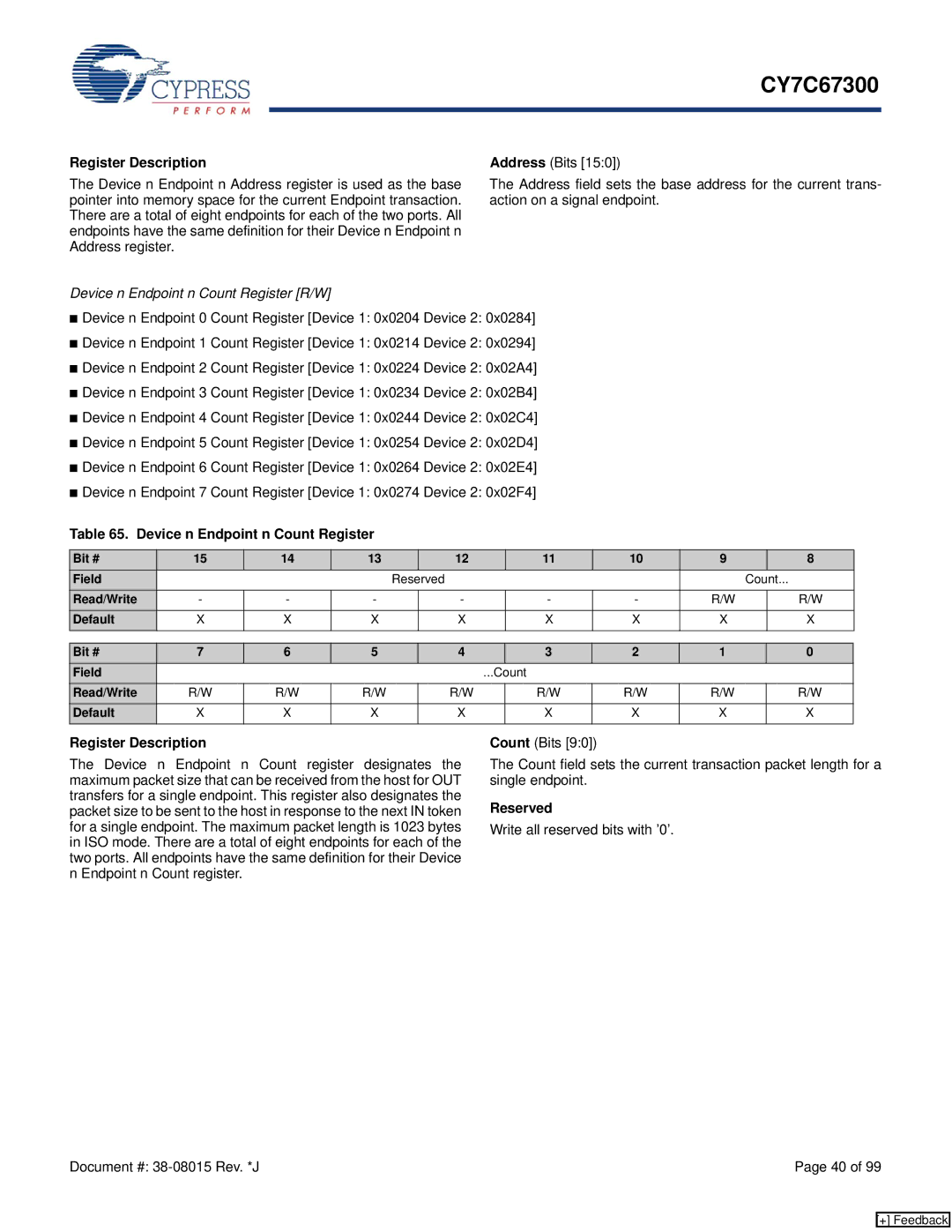

Device n Endpoint n Count Register [R/W]

The Address field sets the base address for the current trans- action on a signal endpoint.

■Device n Endpoint 0 Count Register [Device 1: 0x0204 Device 2: 0x0284]

■Device n Endpoint 1 Count Register [Device 1: 0x0214 Device 2: 0x0294]

■Device n Endpoint 2 Count Register [Device 1: 0x0224 Device 2: 0x02A4]

■Device n Endpoint 3 Count Register [Device 1: 0x0234 Device 2: 0x02B4]

■Device n Endpoint 4 Count Register [Device 1: 0x0244 Device 2: 0x02C4]

■Device n Endpoint 5 Count Register [Device 1: 0x0254 Device 2: 0x02D4]

■Device n Endpoint 6 Count Register [Device 1: 0x0264 Device 2: 0x02E4]

■Device n Endpoint 7 Count Register [Device 1: 0x0274 Device 2: 0x02F4]

Table 65. Device n Endpoint n Count Register

Bit # | 15 | 14 | 13 |

| 12 | 11 | 10 | 9 |

| 8 |

Field |

|

|

| Reserved |

|

|

| Count... | ||

Read/Write | - | - | - |

| - | - | - | R/W |

| R/W |

Default | X | X | X |

| X | X | X | X |

| X |

|

|

|

|

|

|

|

|

|

|

|

Bit # | 7 | 6 | 5 | 4 |

| 3 | 2 | 1 | 0 |

Field |

|

|

|

| ...Count |

|

|

| |

Read/Write | R/W | R/W | R/W | R/W |

| R/W | R/W | R/W | R/W |

Default | X | X | X | X |

| X | X | X | X |

|

|

|

|

|

|

|

|

|

|

Register Description

The Device n Endpoint n Count register designates the maximum packet size that can be received from the host for OUT transfers for a single endpoint. This register also designates the packet size to be sent to the host in response to the next IN token for a single endpoint. The maximum packet length is 1023 bytes in ISO mode. There are a total of eight endpoints for each of the two ports. All endpoints have the same definition for their Device n Endpoint n Count register.

Count (Bits [9:0])

The Count field sets the current transaction packet length for a single endpoint.

Reserved

Write all reserved bits with ’0’.

Document #: | Page 40 of 99 |

[+] Feedback