CY7C67300

Host Port Interface

HPI Features

■

■16 MB/s throughput

■

■Direct memory access (DMA) to internal memory

■Bidirectional Mailbox register

■Byte swapping

■Complete access to internal memory

■Complete control of SIEs through HPI

■Dedicated HPI status register

HPI Pins

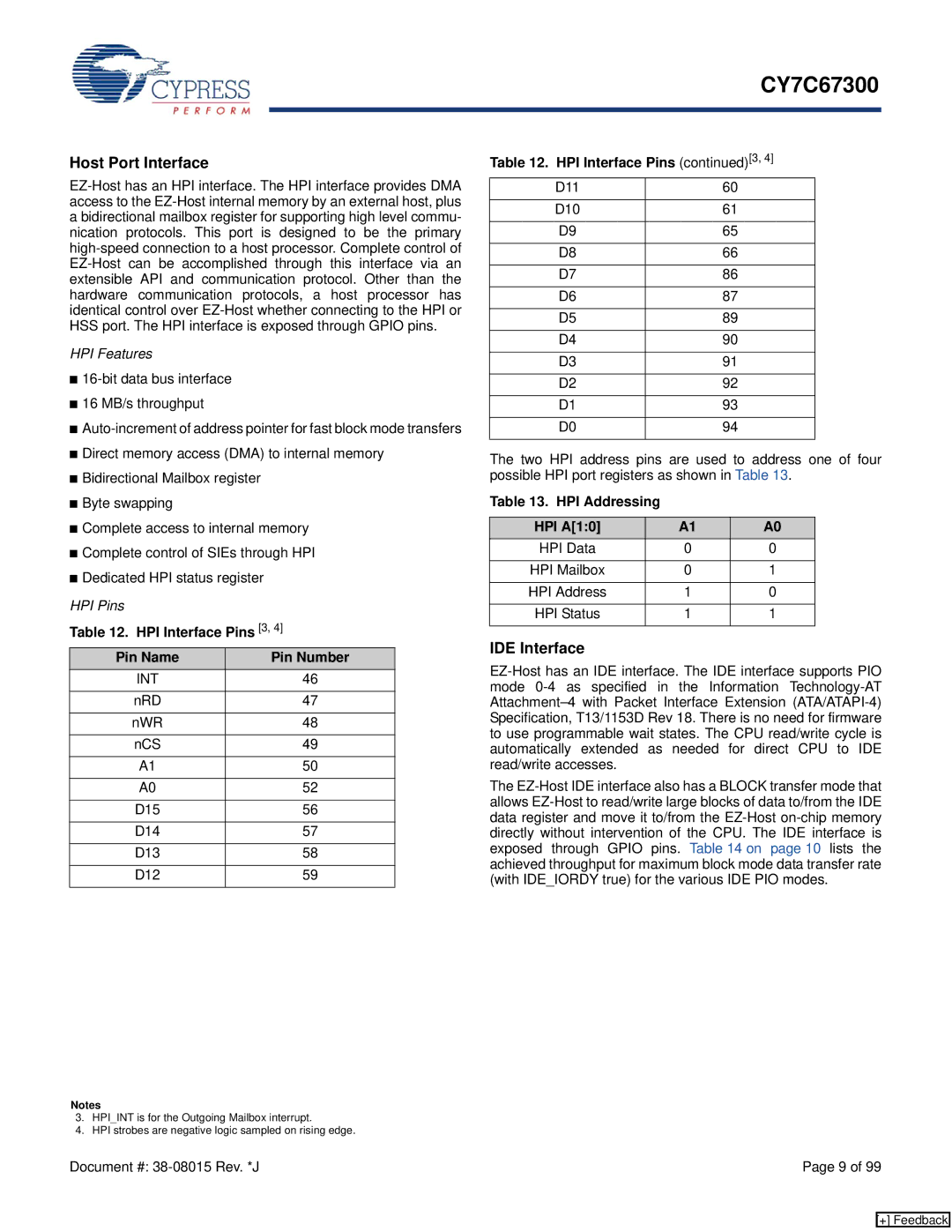

Table 12. HPI Interface Pins [3, 4]

Pin Name | Pin Number |

INT | 46 |

|

|

nRD | 47 |

|

|

nWR | 48 |

|

|

nCS | 49 |

|

|

A1 | 50 |

|

|

A0 | 52 |

|

|

D15 | 56 |

|

|

D14 | 57 |

|

|

D13 | 58 |

|

|

D12 | 59 |

|

|

Table 12. HPI Interface Pins (continued)[3, 4]

D11 | 60 |

|

|

D10 | 61 |

|

|

D9 | 65 |

|

|

D8 | 66 |

|

|

D7 | 86 |

|

|

D6 | 87 |

|

|

D5 | 89 |

|

|

D4 | 90 |

|

|

D3 | 91 |

|

|

D2 | 92 |

|

|

D1 | 93 |

|

|

D0 | 94 |

|

|

The two HPI address pins are used to address one of four possible HPI port registers as shown in Table 13.

Table 13. HPI Addressing

HPI A[1:0] | A1 | A0 |

HPI Data | 0 | 0 |

|

|

|

HPI Mailbox | 0 | 1 |

|

|

|

HPI Address | 1 | 0 |

|

|

|

HPI Status | 1 | 1 |

|

|

|

IDE Interface

The

Notes

3.HPI_INT is for the Outgoing Mailbox interrupt.

4.HPI strobes are negative logic sampled on rising edge.

Document #: | Page 9 of 99 |

[+] Feedback