CY7C67300

Port A SOF/EOP Enable (Bit 0) | Reserved |

The Port A SOF/EOP Enable bit is only applicable in host mode. | Write all reserved bits with ’0’. |

In device mode this bit must be written as ‘0’. In host mode this |

|

bit enables or disables SOFs or EOPs for Port A. Either SOFs or |

|

EOPs are generated depending on the LOA bit in the USB n |

|

Control register when Port A is active. |

|

1: Enable SOFs or EOPs |

|

0: Disable SOFs or EOPs |

|

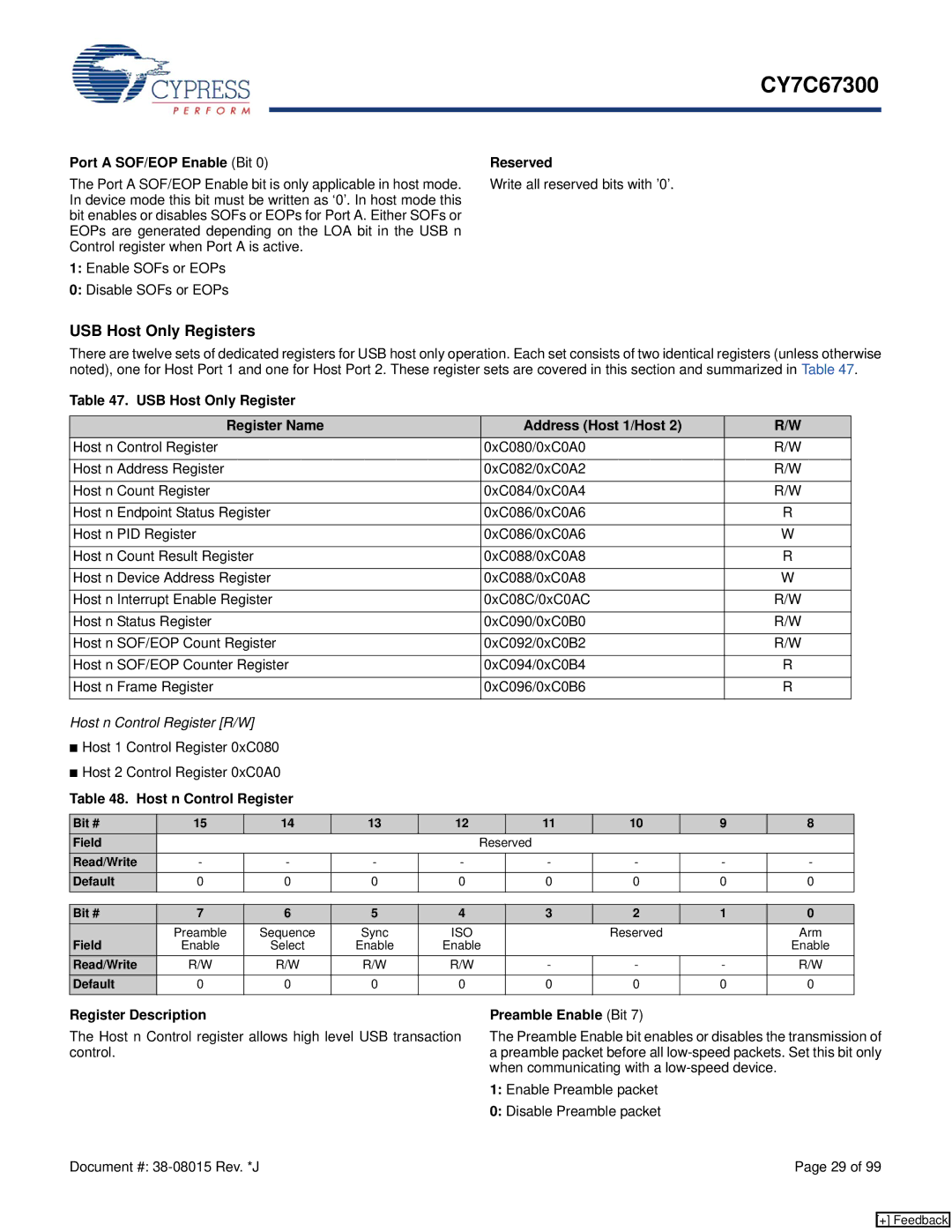

USB Host Only Registers

There are twelve sets of dedicated registers for USB host only operation. Each set consists of two identical registers (unless otherwise noted), one for Host Port 1 and one for Host Port 2. These register sets are covered in this section and summarized in Table 47.

Table 47. USB Host Only Register

Register Name | Address (Host 1/Host 2) | R/W |

Host n Control Register | 0xC080/0xC0A0 | R/W |

|

|

|

Host n Address Register | 0xC082/0xC0A2 | R/W |

|

|

|

Host n Count Register | 0xC084/0xC0A4 | R/W |

|

|

|

Host n Endpoint Status Register | 0xC086/0xC0A6 | R |

|

|

|

Host n PID Register | 0xC086/0xC0A6 | W |

|

|

|

Host n Count Result Register | 0xC088/0xC0A8 | R |

|

|

|

Host n Device Address Register | 0xC088/0xC0A8 | W |

|

|

|

Host n Interrupt Enable Register | 0xC08C/0xC0AC | R/W |

|

|

|

Host n Status Register | 0xC090/0xC0B0 | R/W |

|

|

|

Host n SOF/EOP Count Register | 0xC092/0xC0B2 | R/W |

|

|

|

Host n SOF/EOP Counter Register | 0xC094/0xC0B4 | R |

|

|

|

Host n Frame Register | 0xC096/0xC0B6 | R |

|

|

|

Host n Control Register [R/W]

■Host 1 Control Register 0xC080

■Host 2 Control Register 0xC0A0

Table 48. Host n Control Register

Bit # | 15 | 14 | 13 | 12 |

| 11 | 10 | 9 | 8 |

Field |

|

|

|

| Reserved |

|

|

| |

Read/Write | - | - | - | - |

| - | - | - | - |

Default | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 |

Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

Field | Preamble | Sequence | Sync | ISO |

| Reserved |

| Arm |

Enable | Select | Enable | Enable |

|

|

| Enable | |

Read/Write | R/W | R/W | R/W | R/W | - | - | - | R/W |

Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Register Description

The Host n Control register allows high level USB transaction control.

Preamble Enable (Bit 7)

The Preamble Enable bit enables or disables the transmission of a preamble packet before all

1:Enable Preamble packet

0:Disable Preamble packet

Document #: | Page 29 of 99 |

[+] Feedback