CY7C67300

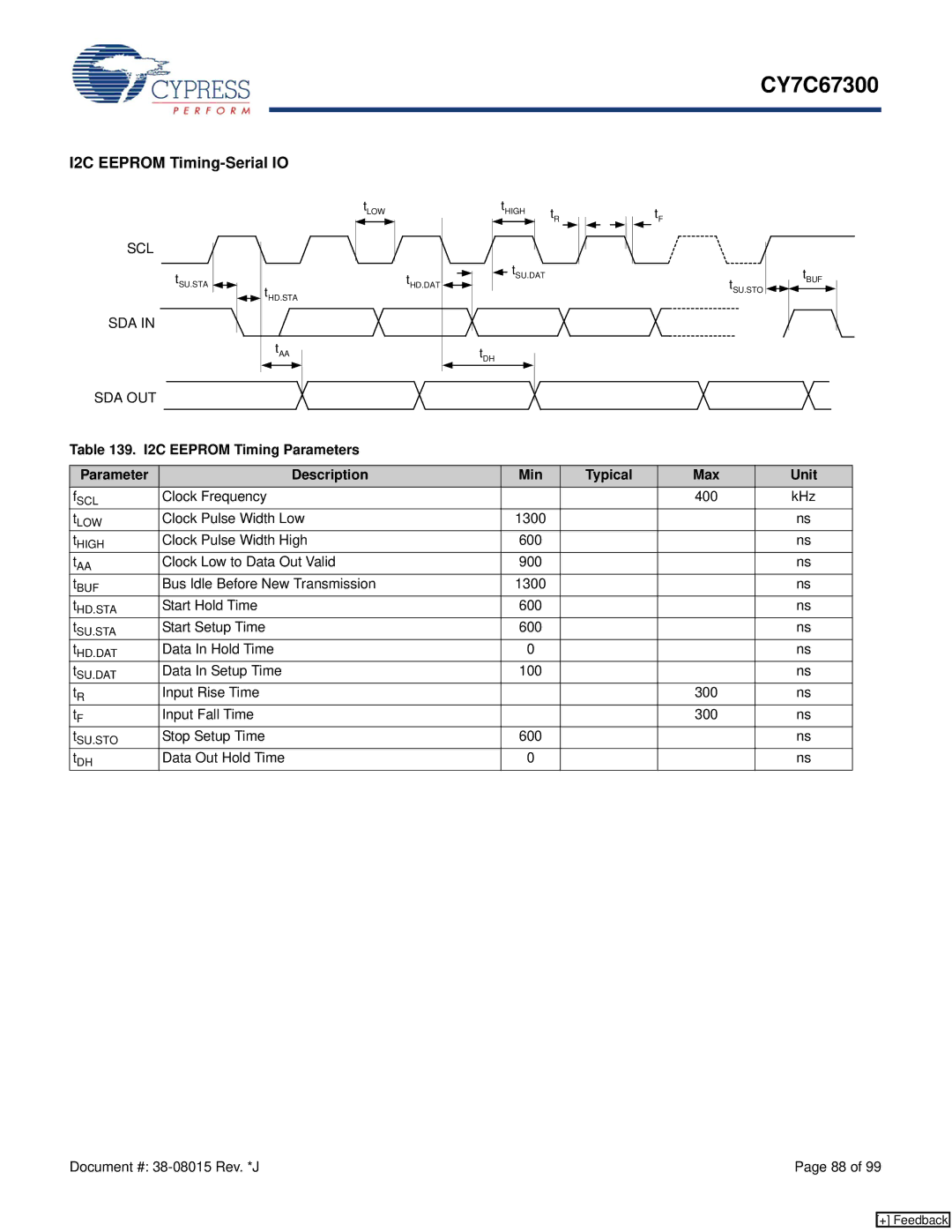

I2C EEPROM |

|

| |

| tLOW | tHIGH | tR |

|

| ||

SCL |

|

|

|

tSU.STA |

| tSU.DAT |

|

tHD.STA | tHD.DAT |

| |

|

|

| |

SDA IN |

|

|

|

| tAA | tDH |

|

SDA OUT

tF

tSU.STO ![]()

![]() tBUF

tBUF ![]()

Table 139. I2C EEPROM Timing Parameters

Parameter | Description | Min | Typical | Max | Unit |

fSCL | Clock Frequency |

|

| 400 | kHz |

tLOW | Clock Pulse Width Low | 1300 |

|

| ns |

tHIGH | Clock Pulse Width High | 600 |

|

| ns |

tAA | Clock Low to Data Out Valid | 900 |

|

| ns |

tBUF | Bus Idle Before New Transmission | 1300 |

|

| ns |

tHD.STA | Start Hold Time | 600 |

|

| ns |

tSU.STA | Start Setup Time | 600 |

|

| ns |

tHD.DAT | Data In Hold Time | 0 |

|

| ns |

tSU.DAT | Data In Setup Time | 100 |

|

| ns |

tR | Input Rise Time |

|

| 300 | ns |

tF | Input Fall Time |

|

| 300 | ns |

tSU.STO | Stop Setup Time | 600 |

|

| ns |

tDH | Data Out Hold Time | 0 |

|

| ns |

Document #: | Page 88 of 99 |

[+] Feedback