CY7C67300

EP2 Interrupt Flag (Bit 2)

The EP2 Interrupt Flag bit indicates if the endpoint two (EP2) Transaction Done interrupt triggered. An EPx Transaction Done interrupt triggers when any of the following responses or events occur in a transaction for the device’s supplied EP: send/receive ACK, send STALL, Timeout occurs, IN Exception Error, or OUT Exception Error. In addition, if the NAK Interrupt Enable bit in the Device n Endpoint Control register is set, this interrupt also triggers when the device NAKs host requests.

1:Interrupt triggered

0:Interrupt did not trigger

EP1 Interrupt Flag (Bit 1)

The EP1 Interrupt Flag bit indicates if the endpoint one (EP1) Transaction Done interrupt triggered. An EPx Transaction Done interrupt triggers when any of the following responses or events occur in a transaction for the device’s supplied EP: send/receive ACK, send STALL, Timeout occurs, IN Exception Error, or OUT Exception Error. In addition, if the NAK Interrupt Enable bit in the

Device n Endpoint Control register is set, this interrupt also triggers when the device NAKs host requests.

1:Interrupt triggered

0:Interrupt did not trigger

EP0 Interrupt Flag (Bit 0)

The EP0 Interrupt Flag bit indicates if the endpoint zero (EP0) Transaction Done interrupt triggered. An EPx Transaction Done interrupt triggers when any of the following responses or events occur in a transaction for the device’s supplied EP: send/receive ACK, send STALL, Timeout occurs, IN Exception Error, or OUT Exception Error. In addition, if the NAK Interrupt Enable bit in the Device n Endpoint Control register is set, this interrupt also triggers when the device NAKs host requests.

1:Interrupt triggered

0:Interrupt did not trigger

Reserved

Write all reserved bits with ’0’.

Device n Frame Number Register [R]

■Device 1 Frame Number Register 0xC092

■Device 2 Frame Number Register 0xC0B2

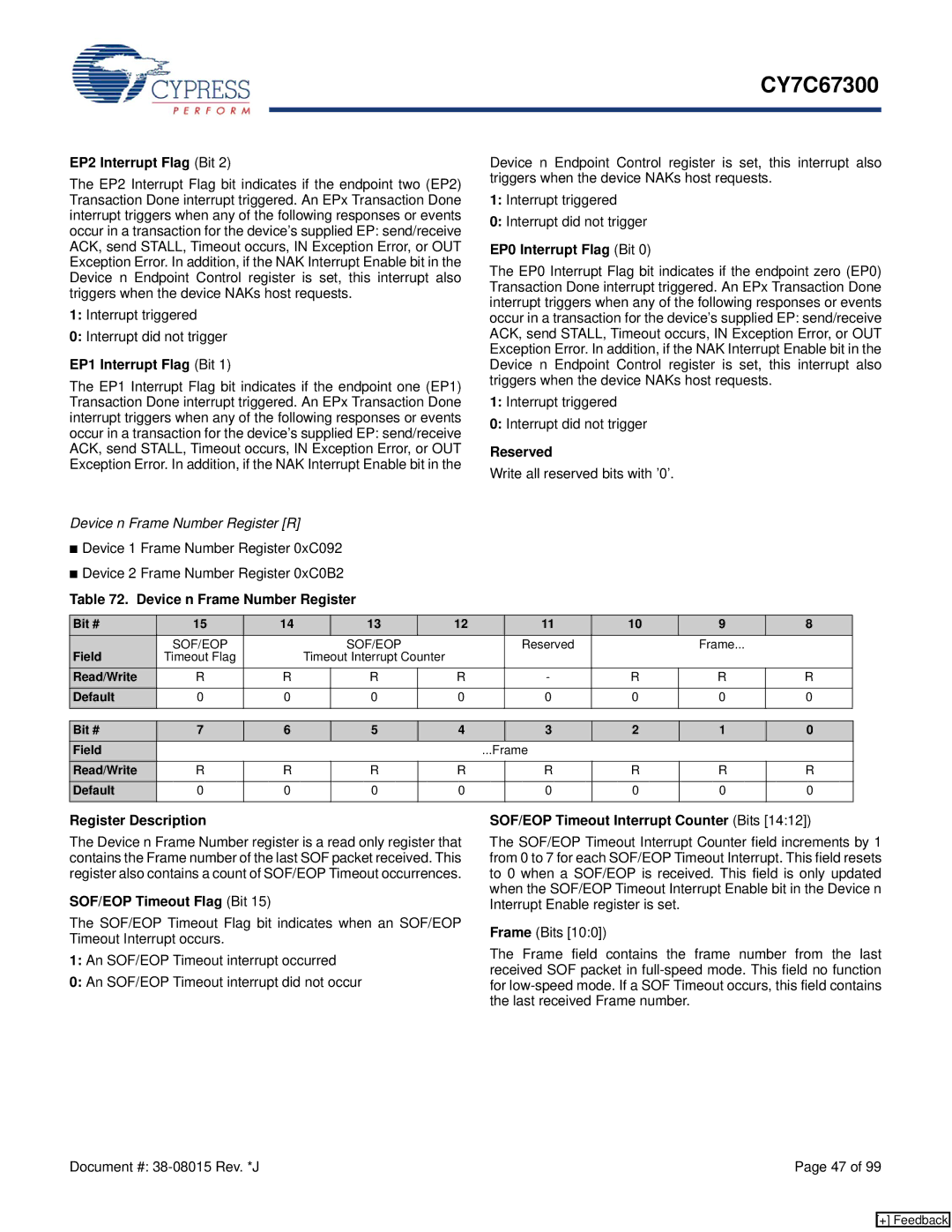

Table 72. Device n Frame Number Register

Bit # | 15 | 14 |

| 13 |

| 12 | 11 | 10 | 9 | 8 |

Field | SOF/EOP |

|

| SOF/EOP |

| Reserved |

| Frame... |

| |

Timeout Flag |

| Timeout Interrupt Counter |

|

|

|

|

| |||

Read/Write | R | R |

| R |

| R | - | R | R | R |

Default | 0 | 0 |

| 0 |

| 0 | 0 | 0 | 0 | 0 |

|

|

|

|

|

|

|

|

|

|

|

Bit # | 7 | 6 | 5 | 4 |

| 3 | 2 | 1 | 0 |

Field |

|

|

|

| ...Frame |

|

|

| |

Read/Write | R | R | R | R |

| R | R | R | R |

Default | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 |

|

|

|

|

|

|

|

|

|

|

Register Description

The Device n Frame Number register is a read only register that contains the Frame number of the last SOF packet received. This register also contains a count of SOF/EOP Timeout occurrences.

SOF/EOP Timeout Flag (Bit 15)

The SOF/EOP Timeout Flag bit indicates when an SOF/EOP Timeout Interrupt occurs.

1:An SOF/EOP Timeout interrupt occurred

0:An SOF/EOP Timeout interrupt did not occur

SOF/EOP Timeout Interrupt Counter (Bits [14:12])

The SOF/EOP Timeout Interrupt Counter field increments by 1 from 0 to 7 for each SOF/EOP Timeout Interrupt. This field resets to 0 when a SOF/EOP is received. This field is only updated when the SOF/EOP Timeout Interrupt Enable bit in the Device n Interrupt Enable register is set.

Frame (Bits [10:0])

The Frame field contains the frame number from the last received SOF packet in

Document #: | Page 47 of 99 |

[+] Feedback