CY7C67300

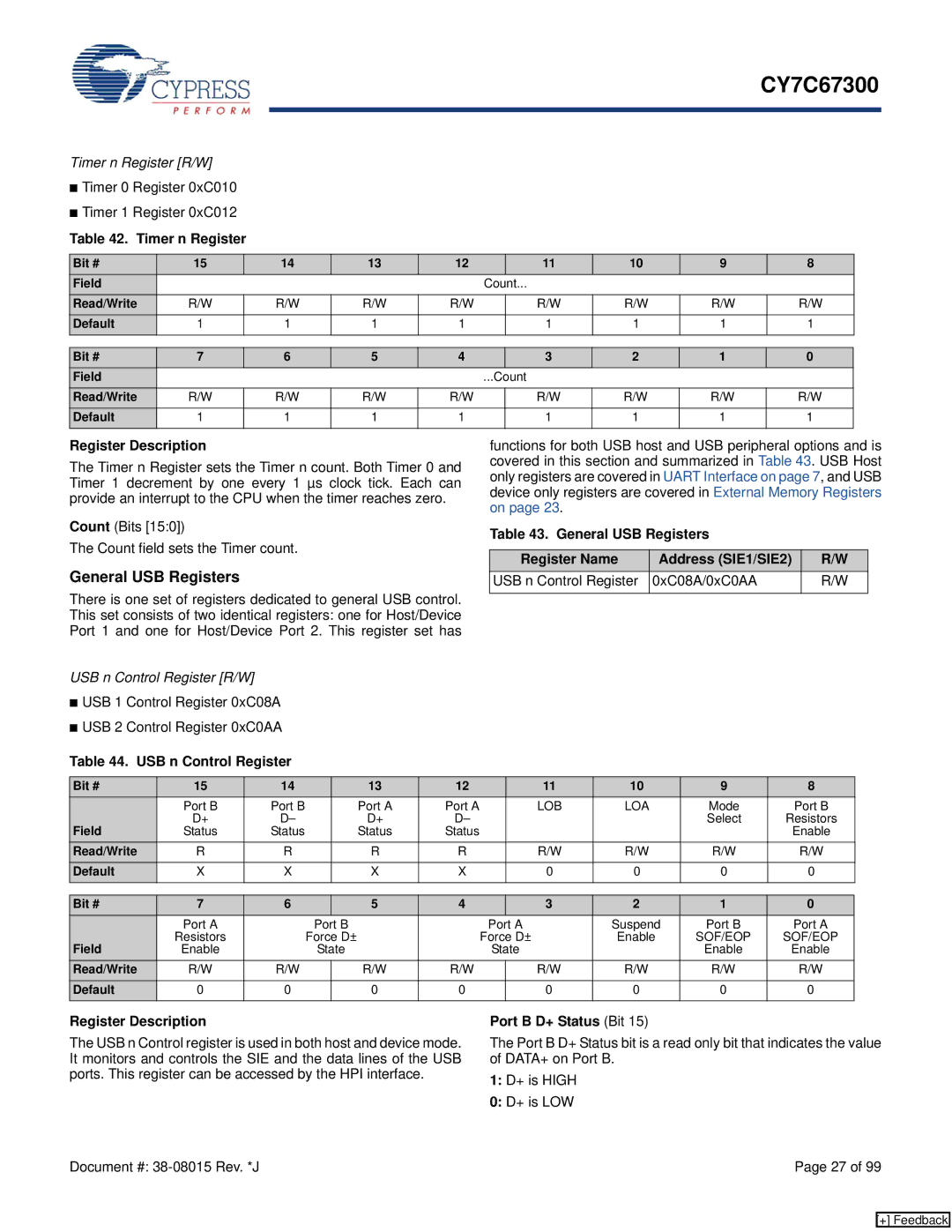

Timer n Register [R/W]

■Timer 0 Register 0xC010

■Timer 1 Register 0xC012

Table 42. Timer n Register

Bit # | 15 | 14 | 13 | 12 |

| 11 | 10 | 9 | 8 |

Field |

|

|

|

| Count... |

|

|

| |

Read/Write | R/W | R/W | R/W | R/W |

| R/W | R/W | R/W | R/W |

Default | 1 | 1 | 1 | 1 |

| 1 | 1 | 1 | 1 |

|

|

|

|

|

|

|

|

|

|

Bit # | 7 | 6 | 5 | 4 |

| 3 | 2 | 1 | 0 |

Field |

|

|

|

| ...Count |

|

|

| |

Read/Write | R/W | R/W | R/W | R/W |

| R/W | R/W | R/W | R/W |

Default | 1 | 1 | 1 | 1 |

| 1 | 1 | 1 | 1 |

|

|

|

|

|

|

|

|

|

|

Register Description

The Timer n Register sets the Timer n count. Both Timer 0 and Timer 1 decrement by one every 1 µs clock tick. Each can provide an interrupt to the CPU when the timer reaches zero.

Count (Bits [15:0])

The Count field sets the Timer count.

General USB Registers

There is one set of registers dedicated to general USB control. This set consists of two identical registers: one for Host/Device Port 1 and one for Host/Device Port 2. This register set has

USB n Control Register [R/W]

■USB 1 Control Register 0xC08A

■USB 2 Control Register 0xC0AA

Table 44. USB n Control Register

functions for both USB host and USB peripheral options and is covered in this section and summarized in Table 43. USB Host only registers are covered in UART Interface on page 7, and USB device only registers are covered in External Memory Registers on page 23.

Table 43. General USB Registers

Register Name | Address (SIE1/SIE2) | R/W |

USB n Control Register | 0xC08A/0xC0AA | R/W |

|

|

|

Bit # | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| Port B | Port B | Port A | Port A | LOB | LOA | Mode | Port B |

Field | D+ | D– | D+ | D– |

|

| Select | Resistors |

Status | Status | Status | Status |

|

|

| Enable | |

Read/Write | R | R | R | R | R/W | R/W | R/W | R/W |

Default | X | X | X | X | 0 | 0 | 0 | 0 |

|

|

|

|

|

|

|

|

|

Bit # | 7 | 6 |

| 5 | 4 |

| 3 | 2 | 1 | 0 |

| Port A |

| Port B | Port A |

| Suspend | Port B | Port A | ||

Field | Resistors |

| Force D± | Force D± |

| Enable | SOF/EOP | SOF/EOP | ||

Enable |

| State | State |

|

| Enable | Enable | |||

Read/Write | R/W | R/W |

| R/W | R/W |

| R/W | R/W | R/W | R/W |

Default | 0 | 0 |

| 0 | 0 |

| 0 | 0 | 0 | 0 |

|

|

|

|

|

|

|

|

|

|

|

Register Description

The USB n Control register is used in both host and device mode. It monitors and controls the SIE and the data lines of the USB ports. This register can be accessed by the HPI interface.

Port B D+ Status (Bit 15)

The Port B D+ Status bit is a read only bit that indicates the value of DATA+ on Port B.

1:D+ is HIGH

0:D+ is LOW

Document #: | Page 27 of 99 |

[+] Feedback