CY7C67300

Register Description

The SPI Receive Count register designates the block byte length for the SPI receive DMA transfer.

Count (Bits [10:0])

The Count field sets the count for the SPI receive DMA transfer.

Reserved

Write all reserved bits with ’0’.

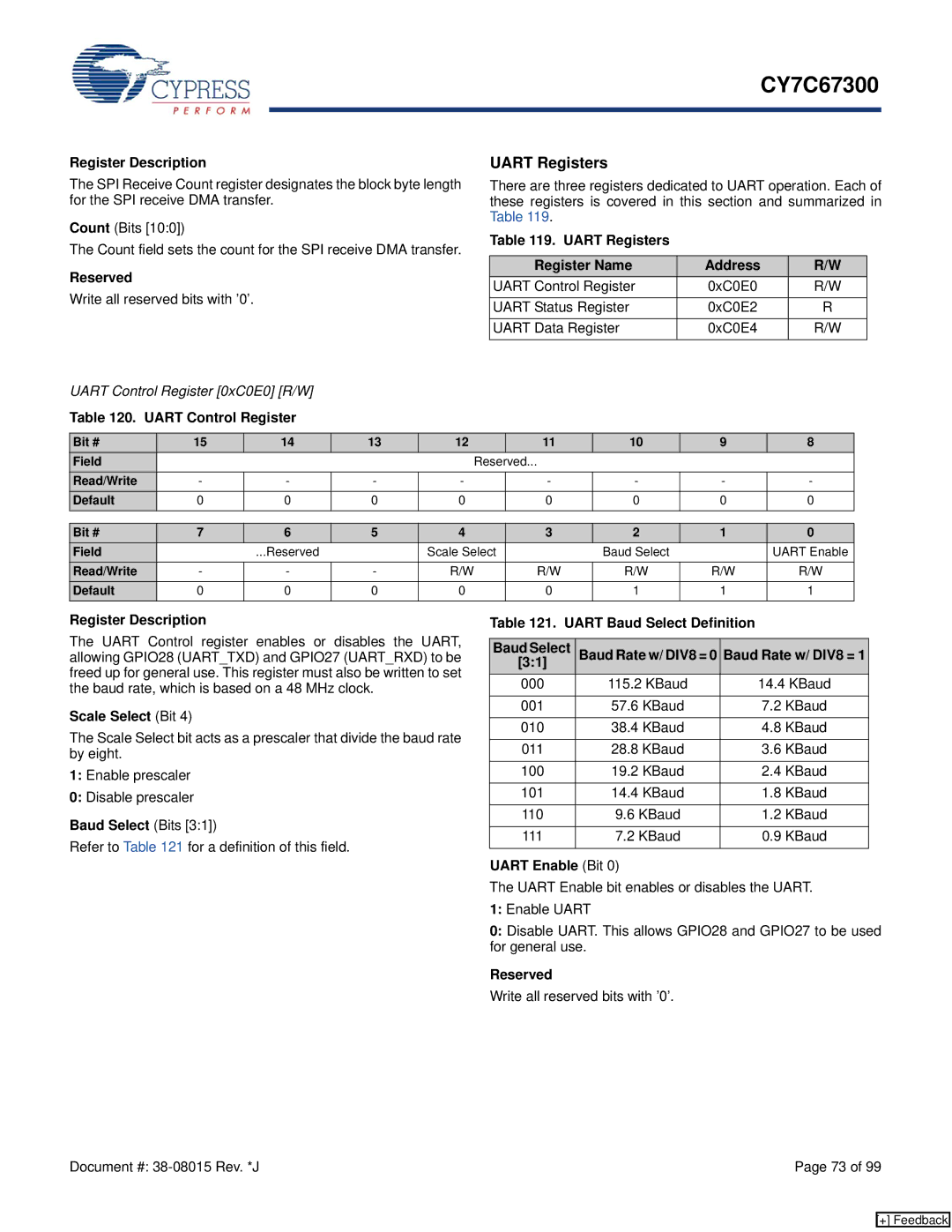

UART Control Register [0xC0E0] [R/W]

Table 120. UART Control Register

UART Registers

There are three registers dedicated to UART operation. Each of these registers is covered in this section and summarized in Table 119.

Table 119. UART Registers

Register Name | Address | R/W |

UART Control Register | 0xC0E0 | R/W |

UART Status Register | 0xC0E2 | R |

UART Data Register | 0xC0E4 | R/W |

Bit # | 15 | 14 | 13 | 12 |

| 11 | 10 | 9 | 8 |

Field |

|

|

|

| Reserved... |

|

|

| |

Read/Write | - | - | - | - |

| - | - | - | - |

Default | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 |

Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

Field |

| ...Reserved |

| Scale Select |

| Baud Select |

| UART Enable |

Read/Write | - | - | - | R/W | R/W | R/W | R/W | R/W |

Default | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 |

Register Description

The UART Control register enables or disables the UART, allowing GPIO28 (UART_TXD) and GPIO27 (UART_RXD) to be freed up for general use. This register must also be written to set the baud rate, which is based on a 48 MHz clock.

Scale Select (Bit 4)

The Scale Select bit acts as a prescaler that divide the baud rate by eight.

1:Enable prescaler

0:Disable prescaler

Baud Select (Bits [3:1])

Refer to Table 121 for a definition of this field.

Table 121. UART Baud Select Definition

Baud Select | Baud Rate w/ DIV8 = 0 | Baud Rate w/ DIV8 = 1 |

[3:1] |

|

|

000 | 115.2 KBaud | 14.4 KBaud |

|

|

|

001 | 57.6 KBaud | 7.2 KBaud |

|

|

|

010 | 38.4 KBaud | 4.8 KBaud |

|

|

|

011 | 28.8 KBaud | 3.6 KBaud |

|

|

|

100 | 19.2 KBaud | 2.4 KBaud |

|

|

|

101 | 14.4 KBaud | 1.8 KBaud |

|

|

|

110 | 9.6 KBaud | 1.2 KBaud |

|

|

|

111 | 7.2 KBaud | 0.9 KBaud |

|

|

|

UART Enable (Bit 0)

The UART Enable bit enables or disables the UART.

1:Enable UART

0:Disable UART. This allows GPIO28 and GPIO27 to be used for general use.

Reserved

Write all reserved bits with ’0’.

Document #: | Page 73 of 99 |

[+] Feedback