CHAPTER 2

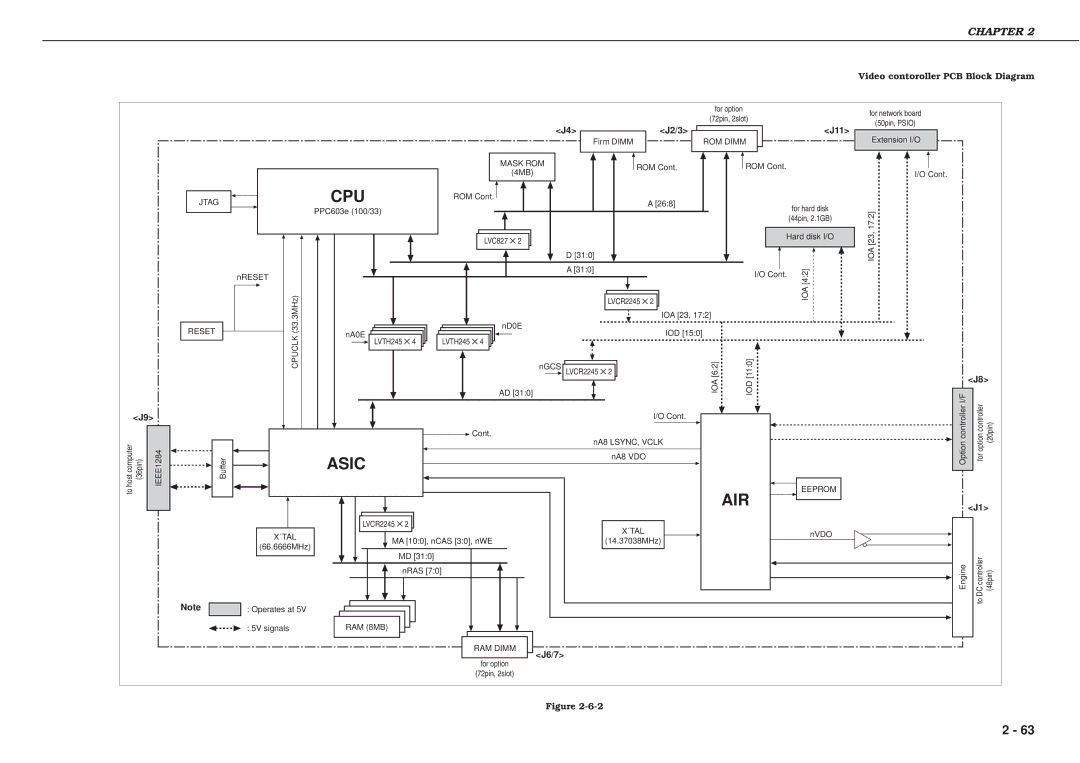

Video contoroller PCB Block Diagram

|

|

|

|

|

|

| for option |

| for network board |

|

| |

|

|

|

|

|

|

| (72pin, 2slot) |

|

|

| ||

|

|

|

|

|

|

|

| (50pin, PSIO) |

|

| ||

|

|

|

|

| <J4> | <J2/3> |

| <J11> |

|

| ||

|

|

|

|

|

| Extension I/O |

|

| ||||

|

|

|

|

|

| Firm DIMM | ROM DIMM |

|

|

| ||

|

|

|

|

| MASK ROM | ROM Cont. | ROM Cont. |

|

|

|

| |

|

|

|

|

| (4MB) |

| I/O Cont. |

|

| |||

|

|

|

|

|

|

|

|

|

|

| ||

|

| JTAG |

| CPU | ROM Cont. |

| A [26:8] |

|

|

|

|

|

|

|

|

|

|

| for hard disk |

|

|

| |||

|

|

|

| PPC603e (100/33) |

|

|

|

| [23, 17:2] |

|

| |

|

|

|

|

|

|

|

| (44pin, 2.1GB) |

|

| ||

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

| LVC827 ✕ 2 |

|

| Hard disk I/O |

|

| ||

|

|

|

|

|

| D [31:0] |

|

|

| IOA |

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

| nRESET |

|

| A [31:0] |

| I/O Cont. | [4:2] |

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

| (33.3MHz) |

|

| LVCR2245 ✕ 2 |

| IOA |

|

|

| |

|

|

|

|

|

| IOA [23, 17:2] |

|

|

|

| ||

|

| RESET | nA0E | nD0E |

| IOD [15:0] |

|

|

|

| ||

|

|

|

|

|

|

|

| |||||

|

| CPUCLK | LVTH245 ✕ 4 |

|

|

|

|

|

| |||

|

|

| LVTH245 ✕ 4 |

|

|

|

|

|

|

| ||

|

|

|

| nGCS | LVCR2245 ✕ 2 | [6:2] | [11:0] |

|

| <J8> | ||

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

| IOA | IOD |

|

| ||

|

|

|

|

| AD [31:0] |

|

| I/F |

|

| ||

|

|

|

|

|

|

|

| for option controller |

| |||

| <J9> |

|

|

|

|

| I/O Cont. |

|

| Option controller | (20pin) | |

|

|

|

|

| Cont. | nA8 LSYNC, VCLK |

|

| ||||

host computer |

|

|

|

|

|

|

| |||||

(36pin) | IEEE1284 | Buffer | ASIC |

| nA8 VDO |

|

|

| ||||

|

|

|

|

| ||||||||

|

|

|

|

| EEPROM | |||||||

to |

|

|

|

|

|

|

| AIR |

|

|

| |

|

|

|

|

|

|

|

|

|

| <J1> | ||

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

| LVCR2245 ✕ 2 |

| X´TAL |

|

|

|

|

|

|

|

|

| X´TAL |

|

|

|

| nVDO |

|

|

| |

|

|

| MA [10:0], nCAS [3:0], nWE | (14.37038MHz) |

|

|

|

| ||||

|

|

|

|

|

|

|

| |||||

|

|

| (66.6666MHz) |

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

| MD [31:0] |

|

|

|

|

|

| DC controller |

|

|

|

|

| nRAS [7:0] |

|

|

|

|

| Engine | (48pin) | |

|

|

|

|

|

|

|

|

|

| |||

|

| Note | : Operates at 5V |

|

|

|

|

|

|

| to |

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

| : 5V signals | RAM (8MB) |

|

|

|

|

|

|

|

|

|

|

|

|

| RAM DIMM |

|

|

|

|

|

|

|

|

|

|

|

| <J6/7> |

|

|

|

|

|

|

|

|

|

|

|

| for option |

|

|

|

|

|

|

|

|

|

|

|

| (72pin, 2slot) |

|

|

|

|

|

|

|

|

|

|

|

| Figure |

|

|

|

|

|

| |

2 - 63