Messages and Beep Codes

Whenever a recoverable error occurs during POST, BIOS displays a message on the video display screen and causes the speaker to beep twice as the message appears. BIOS also issues a beep code (one long tone followed by two short tones) during POST if the video configuration fails or if an external ROM module does not checksum to zero.

At the beginning of each POST test routine, the BIOS outputs the test point error code to I/O address 80h. If the BIOS detects a terminal error condition, it halts POST after issuing a terminal error beep code signifying the test point code and attempting to display the test point error code on the upper left corner of the display screen. BIOS derives the beep code from the test point error code.

For example, a test point error code of 16 is indicated by a

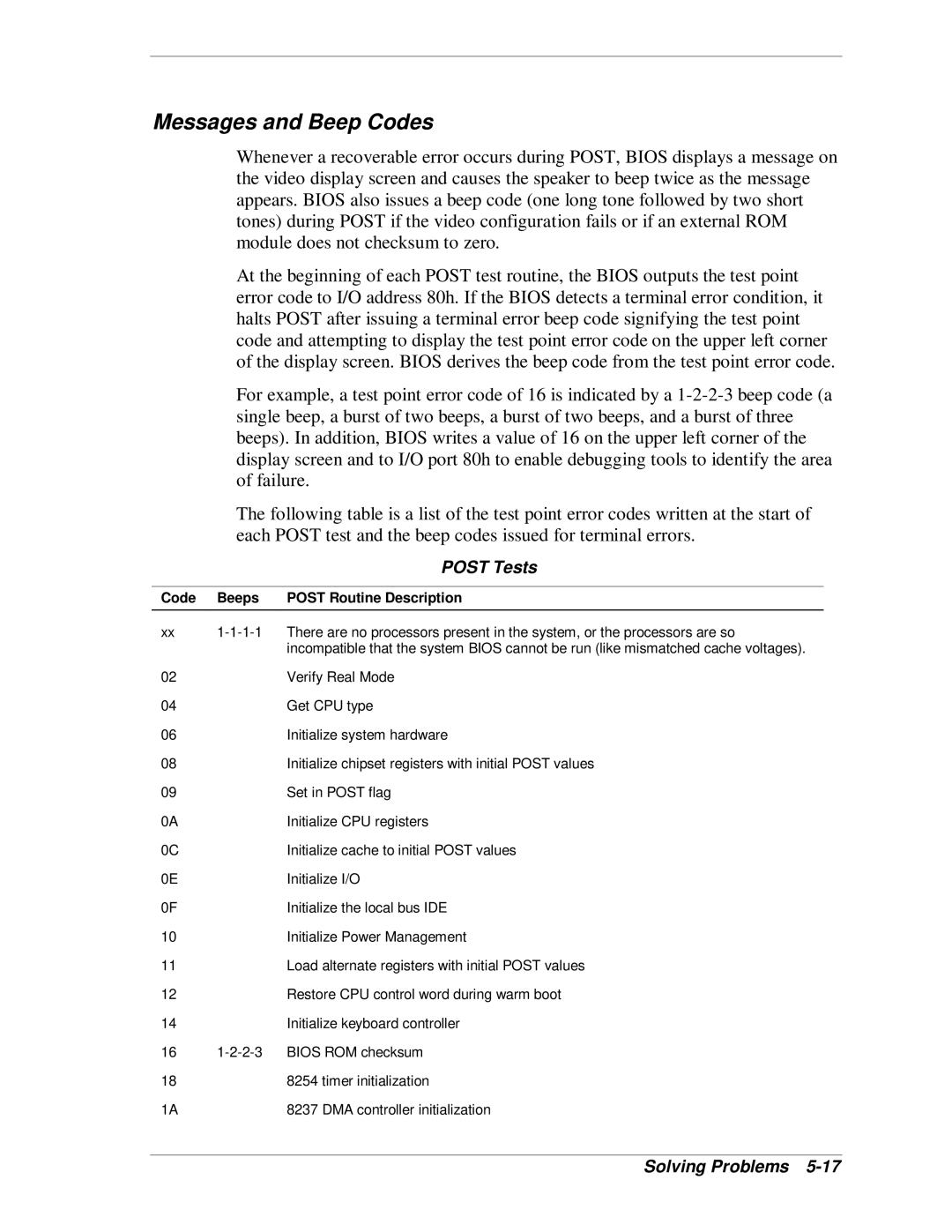

The following table is a list of the test point error codes written at the start of each POST test and the beep codes issued for terminal errors.

POST Tests

Code Beeps POST Routine Description

xx

02 | Verify Real Mode |

04 | Get CPU type |

06 | Initialize system hardware |

08 | Initialize chipset registers with initial POST values |

09 | Set in POST flag |

0A | Initialize CPU registers |

0C | Initialize cache to initial POST values |

0E | Initialize I/O |

0F | Initialize the local bus IDE |

10 | Initialize Power Management |

11 | Load alternate registers with initial POST values |

12 | Restore CPU control word during warm boot |

14 | Initialize keyboard controller |

16 | |

18 | 8254 timer initialization |

1A | 8237 DMA controller initialization |