|

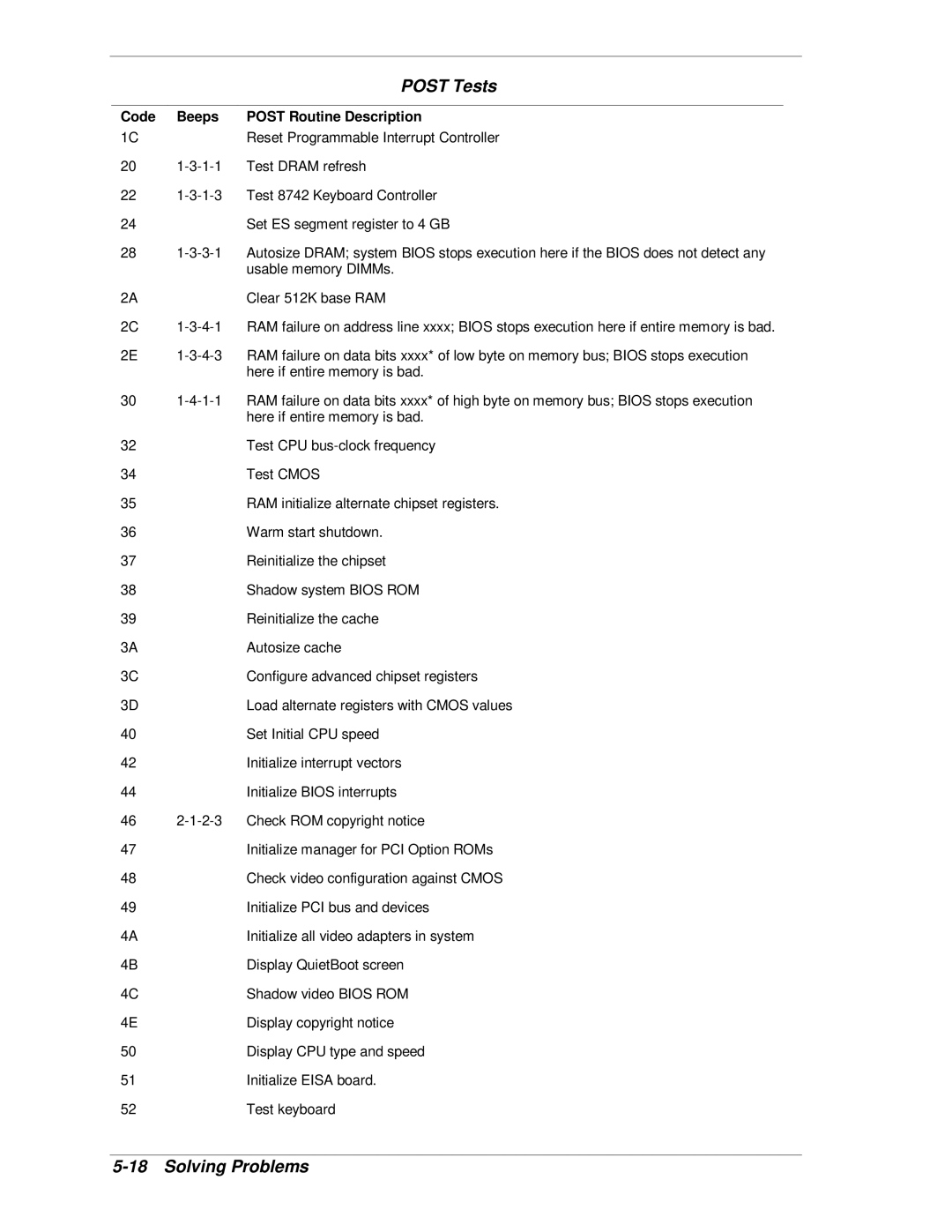

| POST Tests |

|

|

|

Code | Beeps | POST Routine Description |

1C |

| Reset Programmable Interrupt Controller |

20 | Test DRAM refresh | |

22 | Test 8742 Keyboard Controller | |

24 |

| Set ES segment register to 4 GB |

28

2A |

| Clear 512K base RAM |

2C | RAM failure on address line xxxx; BIOS stops execution here if entire memory is bad. | |

2E | RAM failure on data bits xxxx* of low byte on memory bus; BIOS stops execution | |

|

| here if entire memory is bad. |

30

32 | Test CPU |

34 | Test CMOS |

35 | RAM initialize alternate chipset registers. |

36 | Warm start shutdown. |

37 | Reinitialize the chipset |

38 | Shadow system BIOS ROM |

39 | Reinitialize the cache |

3A | Autosize cache |

3C | Configure advanced chipset registers |

3D | Load alternate registers with CMOS values |

40 | Set Initial CPU speed |

42 | Initialize interrupt vectors |

44 | Initialize BIOS interrupts |

46 | |

47 | Initialize manager for PCI Option ROMs |

48 | Check video configuration against CMOS |

49 | Initialize PCI bus and devices |

4A | Initialize all video adapters in system |

4B | Display QuietBoot screen |

4C | Shadow video BIOS ROM |

4E | Display copyright notice |

50 | Display CPU type and speed |

51 | Initialize EISA board. |

52 | Test keyboard |