SMART I/O User’s Manual | Chapter 6 Communications Modules | |||

|

|

|

|

|

|

|

|

|

|

6.2.7.5 Compare Register

This

6.2.7.6 Identification Register

The identification register is read only and fixed at a value of $81.

6.2.7.7 Status Register

The | |||

cleared after a | • DF | : Data Flow | |

• IP | : Interrupt Pending flags | ||

• PE | : Parity Error | • ER1 | : |

• TC | : Transmission Complete | • ER2 | : |

• OL | : Open Line | • MH | : Match |

IP, PE, TC, OL, DF and MH flags are cleared after a reset. ER1 and ER2 represent the current hardware condition

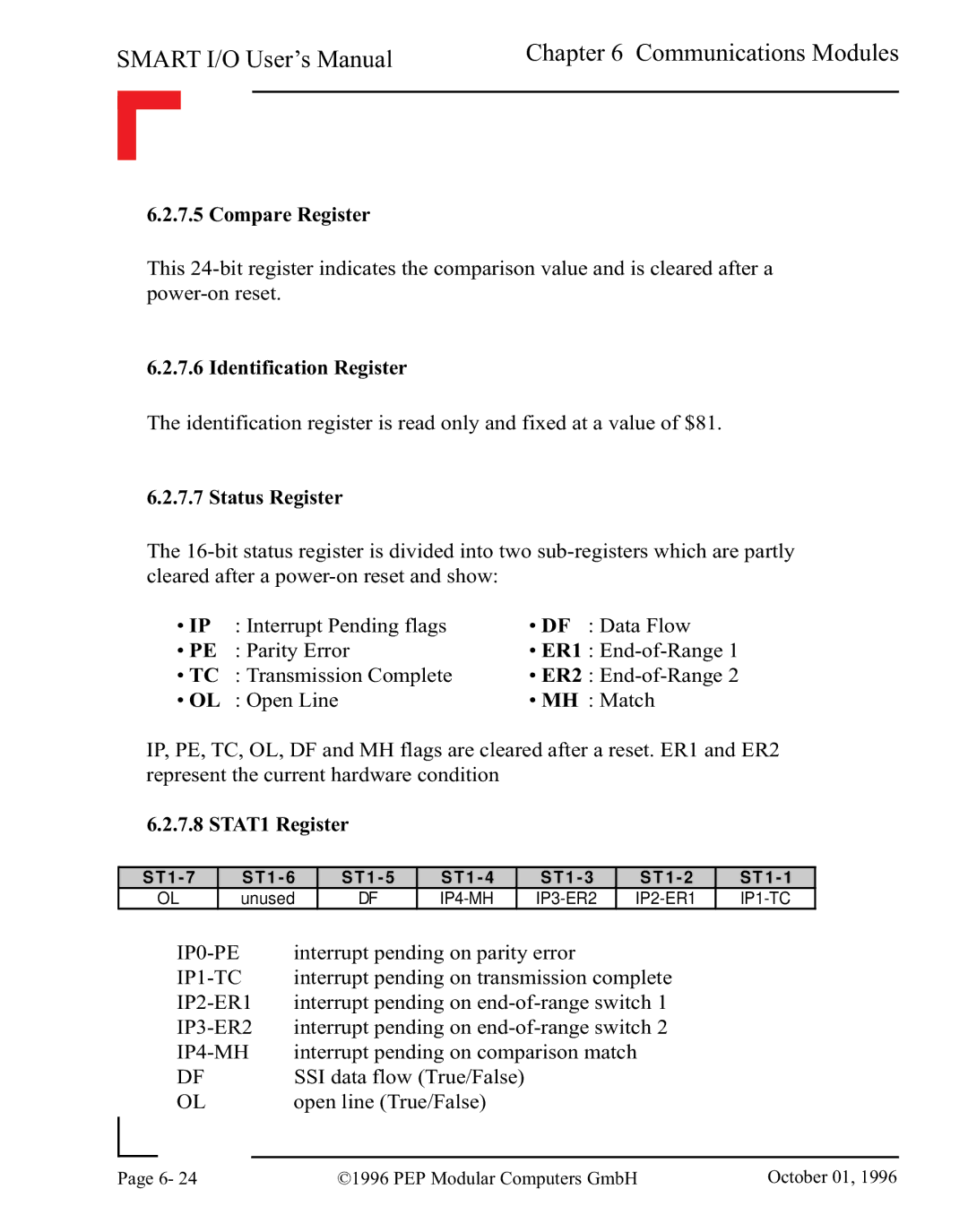

6.2.7.8 STAT1 Register

S T 1 - 7 | S T 1 - 6 | S T 1 - 5 | S T 1 - 4 | S T 1 - 3 | S T 1 - 2 | S T 1 - 1 | |

OL | unused | DF | |||||

| interrupt pending on parity error |

|

| ||||

| interrupt pending on transmission complete |

| |||||

interrupt pending on |

| ||||||

interrupt pending on |

| ||||||

| interrupt pending on comparison match |

| |||||

DF |

| SSI data flow (True/False) |

|

|

| ||

OL |

| open line (True/False) |

|

|

| ||

|

|

|

|

Page | 6- 24 | ©1996 PEP Modular Computers GmbH | October 01, 1996 |

|

|

|