Chapter 6 Communications Modules | SMART I/O User’s Manual | |||

|

|

|

|

|

|

|

|

|

|

•The first HIGH to LOW clock edge (1) in figure 6.2.6.1, triggers the monoflop and allows the current parallel data word present in the parallel

•The crossing of the first LOW to HIGH clock edge after the trigger (2) in figure 6.2.6.1 allows the MSB of the Gray code or binary signal to be transferred.

•With every successive LOW to HIGH transition of the SSI clock, the next bit in the data stream is transferred; this action continues until all the data bits have been transferred. The SSI clock continually retriggers the monoflop forcing it’s output to remain low and thereby preventing unwanted data from being processed.

•When the controller

figure 6.2.6.1.

•The monoflop ceases to be triggered and after a time ‘tm’ returns to a high state as shown in (4) of figure 6.2.6.1. This allows a new data value to be transferred to the parallel

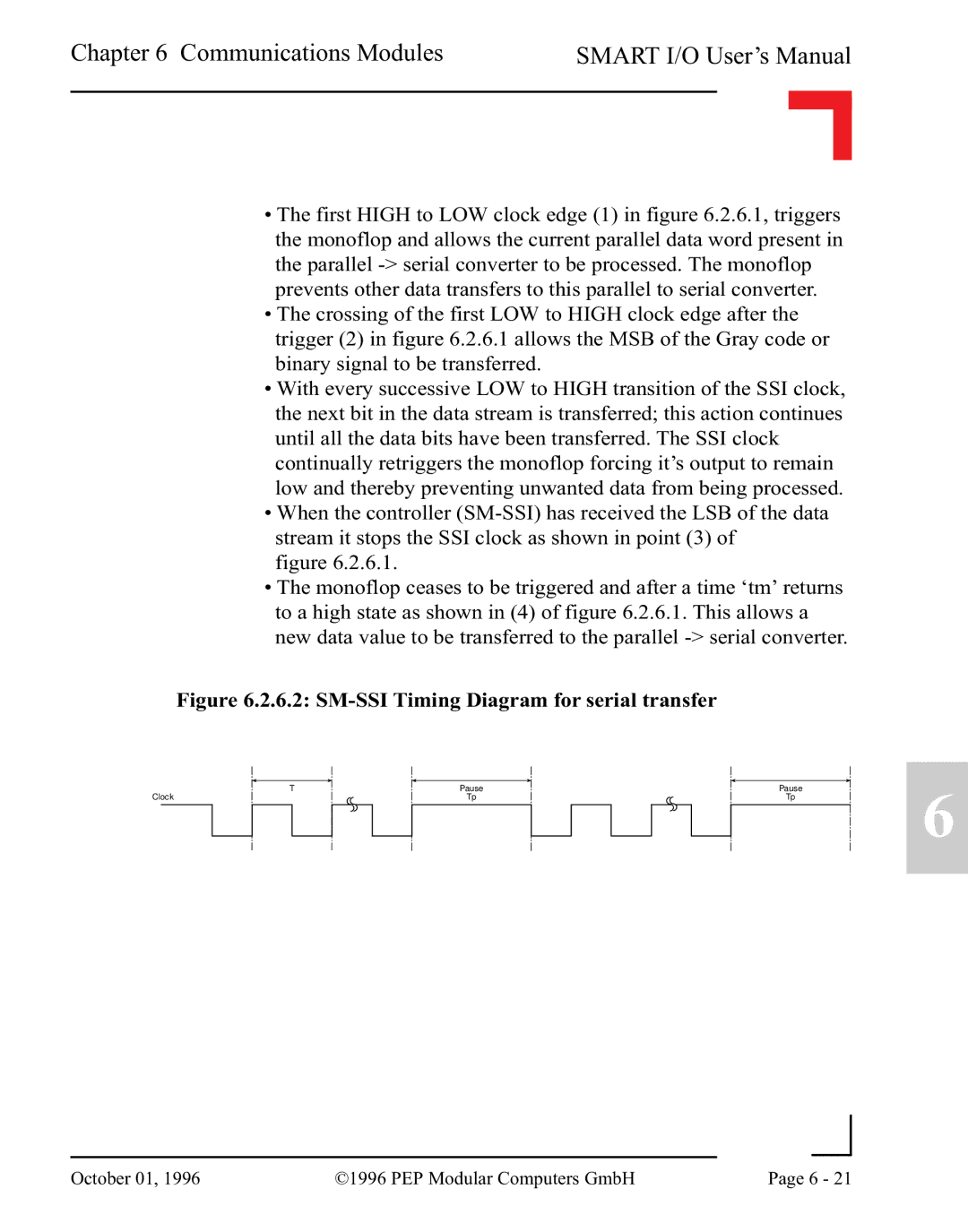

Figure 6.2.6.2: SM-SSI Timing Diagram for serial transfer

T | Pause | Pause |

Clock | Tp | Tp |

6

|

|

|

|

October 01, 1996 | ©1996 PEP Modular Computers GmbH | Page 6 - 21 | |

|

| ||