Chapter 6 Communications Modules | SMART I/O User’s Manual | |||

|

|

|

|

|

|

|

|

|

|

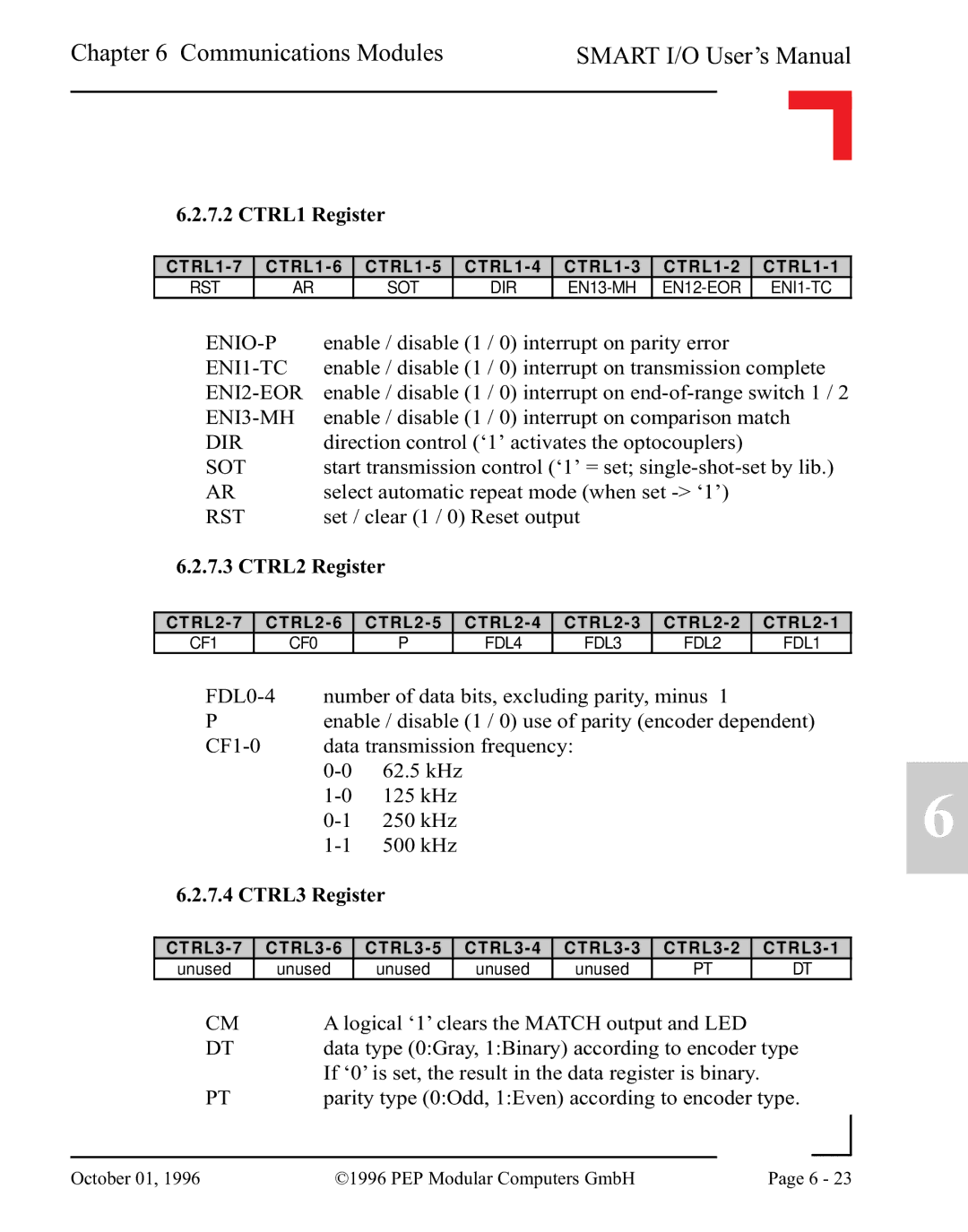

6.2.7.2 CTRL1 Register

C T R L 1 - 7 C T R L 1 - 6 C T R L 1 - 5 C T R L 1 - 4 C T R L 1 - 3 C T R L 1 - 2 C T R L 1 - 1

RST | AR |

| SOT | DIR | |||

| enable / disable (1 / 0) interrupt on parity error |

| |||||

enable / disable (1 / 0) interrupt on transmission complete | |||||||

enable / disable (1 / 0) interrupt on | |||||||

enable / disable (1 / 0) interrupt on comparison match | |||||||

DIR |

| direction control (‘1’ activates the optocouplers) |

| ||||

SOT |

| start transmission control (‘1’ = set; | |||||

AR |

| select automatic repeat mode (when set |

| ||||

RST |

| set / clear (1 / 0) Reset output |

|

| |||

6.2.7.3 CTRL2 Register |

|

|

|

| |||

| |||||||

C T R L 2 - 7 C T R L 2 - 6 C T R L 2 - 5 C T R L 2 - 4 C T R L 2 - 3 C T R L 2 - 2 C T R L 2 - 1 | |||||||

CF1 | CF0 |

| P | FDL4 | FDL3 | FDL2 | FDL1 |

| number of data bits, excluding parity, minus 1 |

| |||||

P |

| enable / disable (1 / 0) use of parity (encoder dependent) | |||||

| data transmission frequency: |

|

| ||||

|

| 62.5 kHz |

|

|

|

| |

|

| 125 kHz |

|

|

|

| |

|

| 250 kHz |

|

|

|

| |

|

| 500 kHz |

|

|

|

| |

6.2.7.4 CTRL3 Register |

|

|

|

| |||

| |||||||

C T R L 3 - 7 C T R L 3 - 6 C T R L 3 - 5 C T R L 3 - 4 C T R L 3 - 3 C T R L 3 - 2 C T R L 3 - 1 | |||||||

unused | unused | unused | unused | unused | PT | DT | |

CM |

| A logical ‘1’ clears the MATCH output and LED |

| ||||

DT |

| data type (0:Gray, 1:Binary) according to encoder type | |||||

PT |

| If ‘0’ is set, the result in the data register is binary. |

| ||||

| parity type (0:Odd, 1:Even) according to encoder type. | ||||||

6

|

|

|

|

October 01, 1996 | ©1996 PEP Modular Computers GmbH | Page 6 - 23 | |

|

| ||