Chapter 6 Communications Modules | SMART I/O User’s Manual | |||

|

|

|

|

|

|

|

|

|

|

Note

Interrupt pending flags (IP0 - IP4) are set by the interrupt source if the corresponding line is not masked in the CTRL1 register. All flags are cleared when the STAT1 register is read.

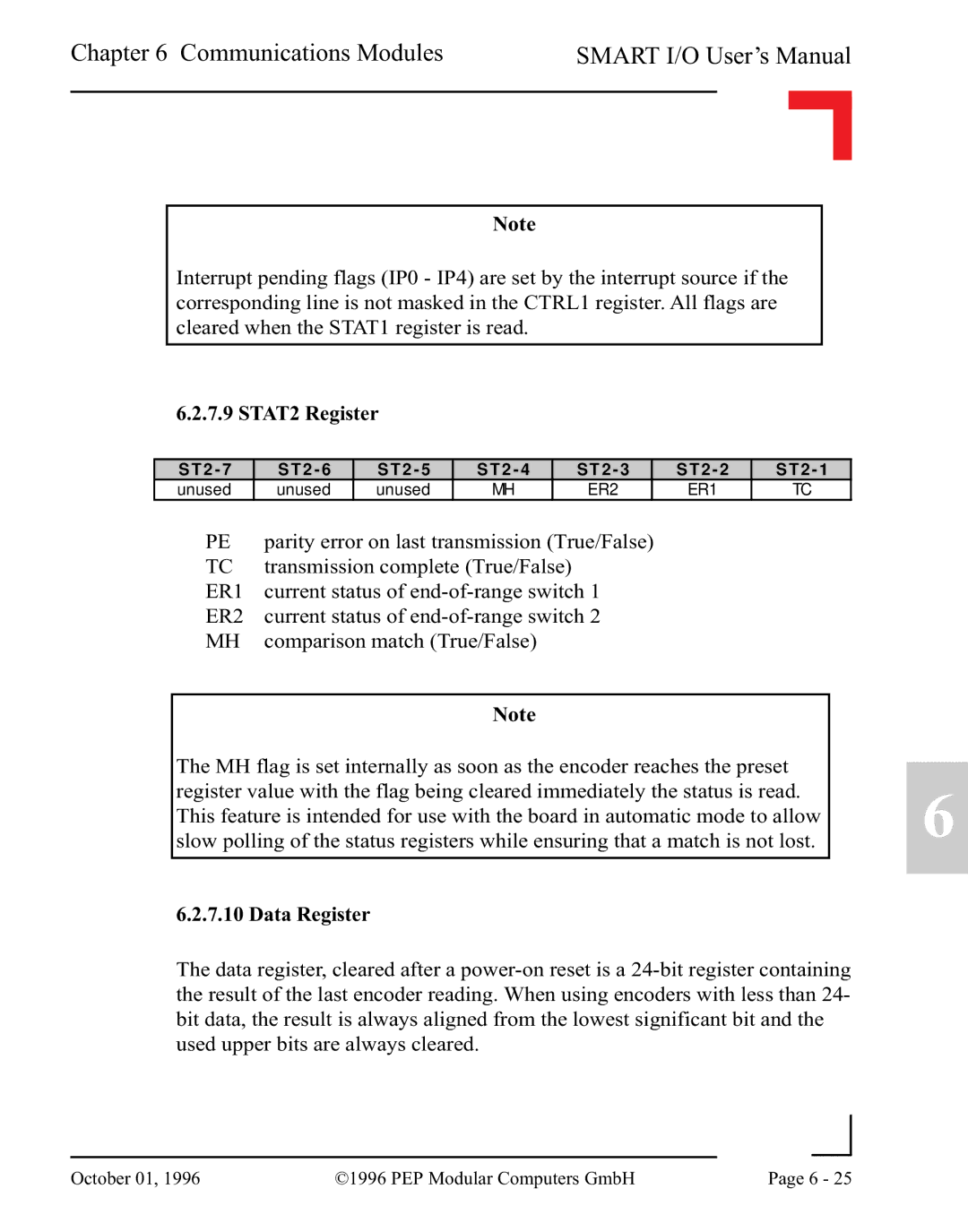

6.2.7.9 STAT2 Register

S T 2 - 7 | S T 2 - 6 | S T 2 - 5 | S T 2 - 4 | S T 2 - 3 | S T 2 - 2 | S T 2 - 1 |

unused | unused | unused | MH | ER2 | ER1 | TC |

PE | parity error on last transmission (True/False) |

|

| |||

TC | transmission complete (True/False) |

|

|

| ||

ER1 | current status of |

|

| |||

ER2 | current status of |

|

| |||

MH | comparison match (True/False) |

|

|

| ||

Note

The MH flag is set internally as soon as the encoder reaches the preset register value with the flag being cleared immediately the status is read. This feature is intended for use with the board in automatic mode to allow slow polling of the status registers while ensuring that a match is not lost.

6.2.7.10 Data Register

The data register, cleared after a

6

|

|

|

|

October 01, 1996 | ©1996 PEP Modular Computers GmbH | Page 6 - 25 | |

|

| ||