Chapter 2 | SMART I/O User’s Manual | |||

|

|

|

|

|

|

|

|

|

|

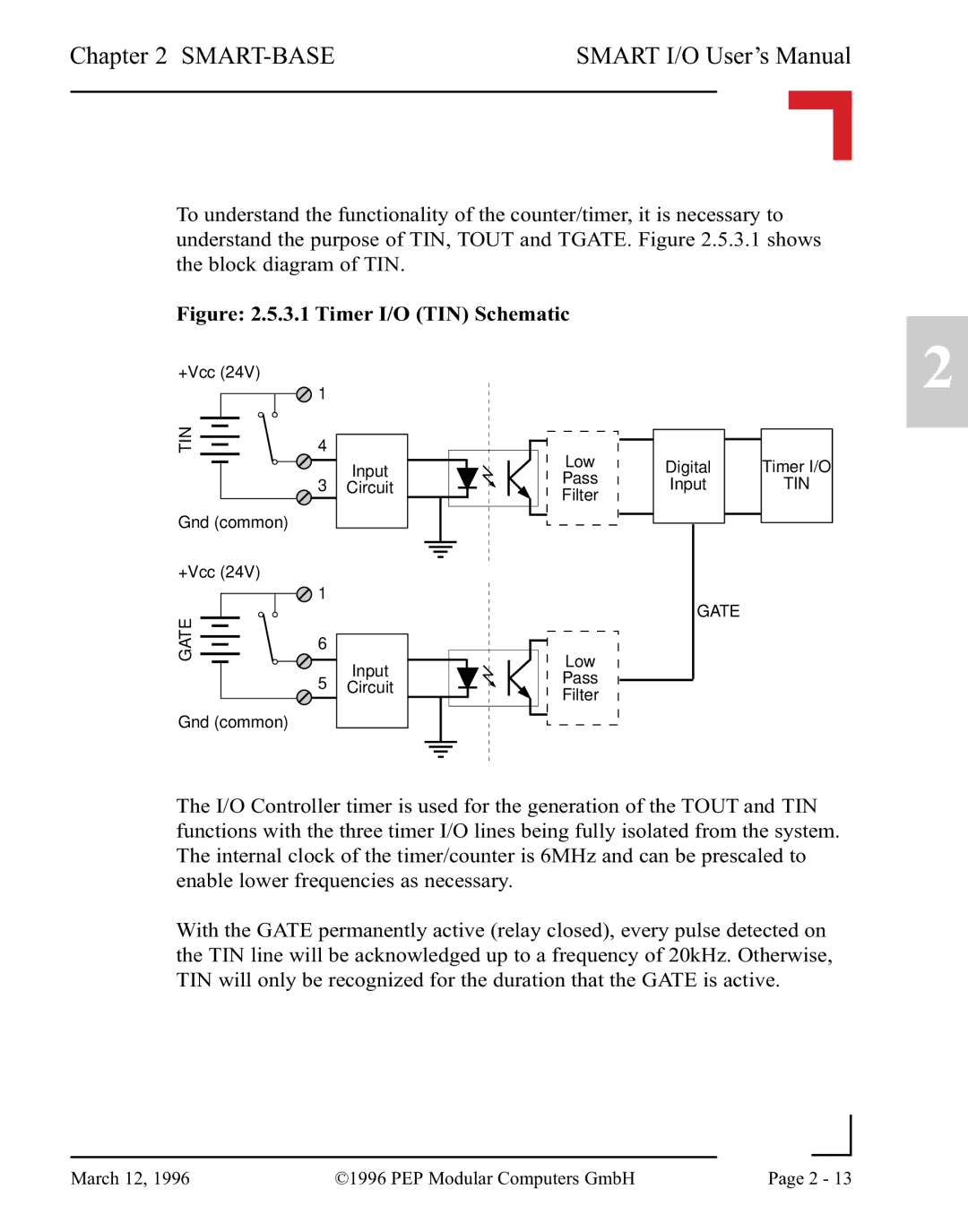

To understand the functionality of the counter/timer, it is necessary to understand the purpose of TIN, TOUT and TGATE. Figure 2.5.3.1 shows the block diagram of TIN.

Figure: 2.5.3.1 Timer I/O (TIN) Schematic

+Vcc (24V)

| 1 |

|

|

TIN | 4 |

| Low |

|

| Input | |

| 3 | Pass | |

| Circuit | ||

| Filter | ||

|

|

| |

Gnd (common) |

|

|

|

+Vcc (24V) |

|

|

|

GATE | 1 |

|

|

6 |

| Low | |

|

| ||

|

| Input | |

| 5 | Pass | |

| Circuit | ||

| Filter | ||

|

|

| |

Gnd (common) |

|

|

|

Digital

Input

GATE

Timer I/O

TIN

2

The I/O Controller timer is used for the generation of the TOUT and TIN functions with the three timer I/O lines being fully isolated from the system. The internal clock of the timer/counter is 6MHz and can be prescaled to enable lower frequencies as necessary.

With the GATE permanently active (relay closed), every pulse detected on the TIN line will be acknowledged up to a frequency of 20kHz. Otherwise, TIN will only be recognized for the duration that the GATE is active.

|

|

|

|

March 12, 1996 | ©1996 PEP Modular Computers GmbH | Page 2 - 13 | |

|

| ||