SMART I/O User’s Manual | Chapter 5 Analog Modules | |||

|

|

|

|

|

|

|

|

|

|

5.1.5 Functional Description

The

5.1.5.1 Input Circuitry

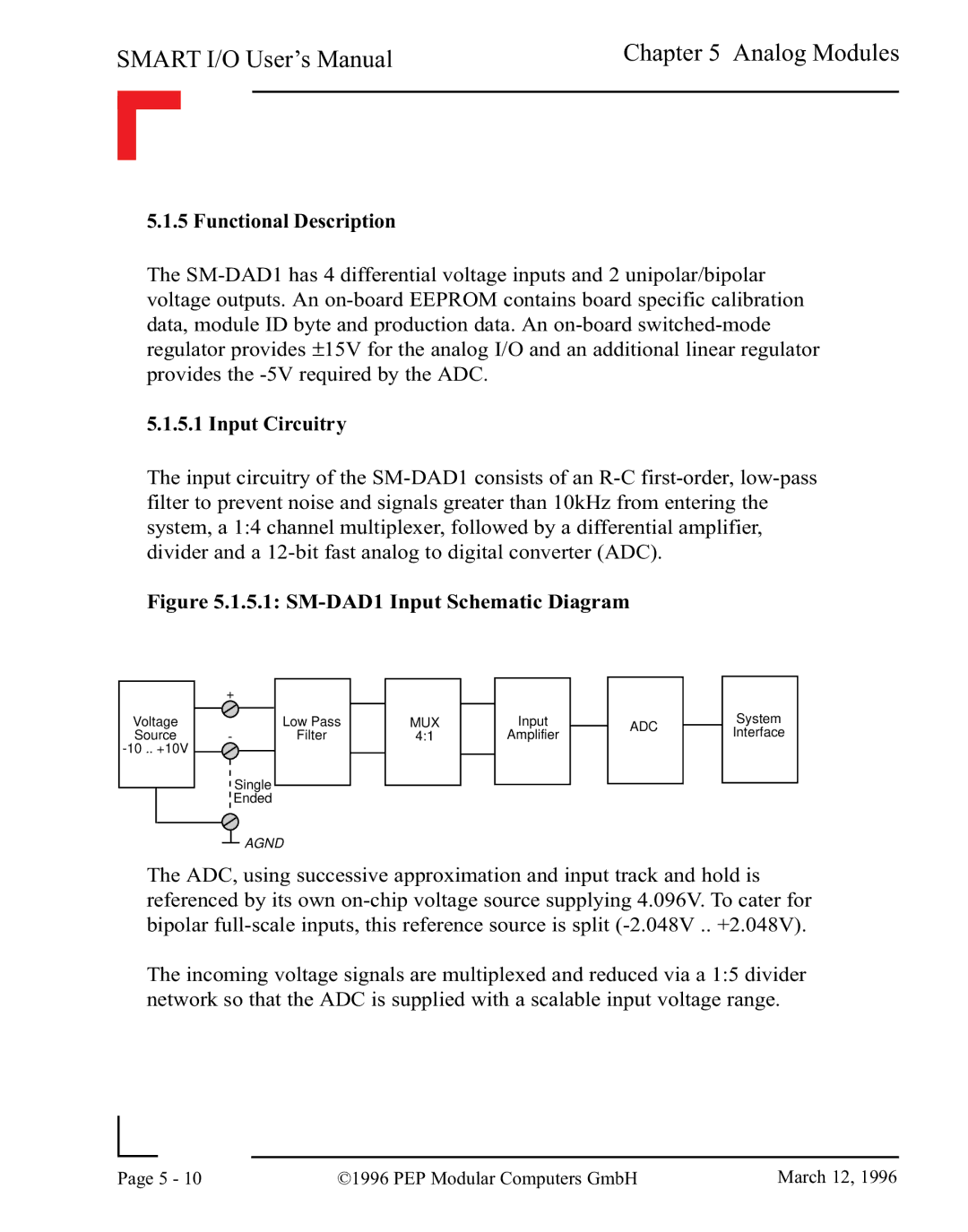

The input circuitry of the

Figure 5.1.5.1: SM-DAD1 Input Schematic Diagram

Voltage

Source

+

Low Pass

-Filter

Single

Ended

![]() AGND

AGND

MUX

4:1

Input

Amplifier

ADC

System

Interface

The ADC, using successive approximation and input track and hold is referenced by its own

The incoming voltage signals are multiplexed and reduced via a 1:5 divider network so that the ADC is supplied with a scalable input voltage range.

|

|

|

|

Page | 5 - 10 | ©1996 PEP Modular Computers GmbH | March 12, 1996 |

|

|

|