SMART I/O User’s Manual | Chapter 2 | |||

|

|

|

|

|

|

|

|

|

|

2.6.8SMTstat Syntax

error_code SMTstat(u_int8 *value);

Description

This function reads the timer status register and clears it if set.

Input

u_int8 *value

Output

error_code

Example

Pointer to a variable in which to place the read value. 0 represents not set, 1 represents set

SUCCESS

or standard

RetVal = SMTstat(buffer);

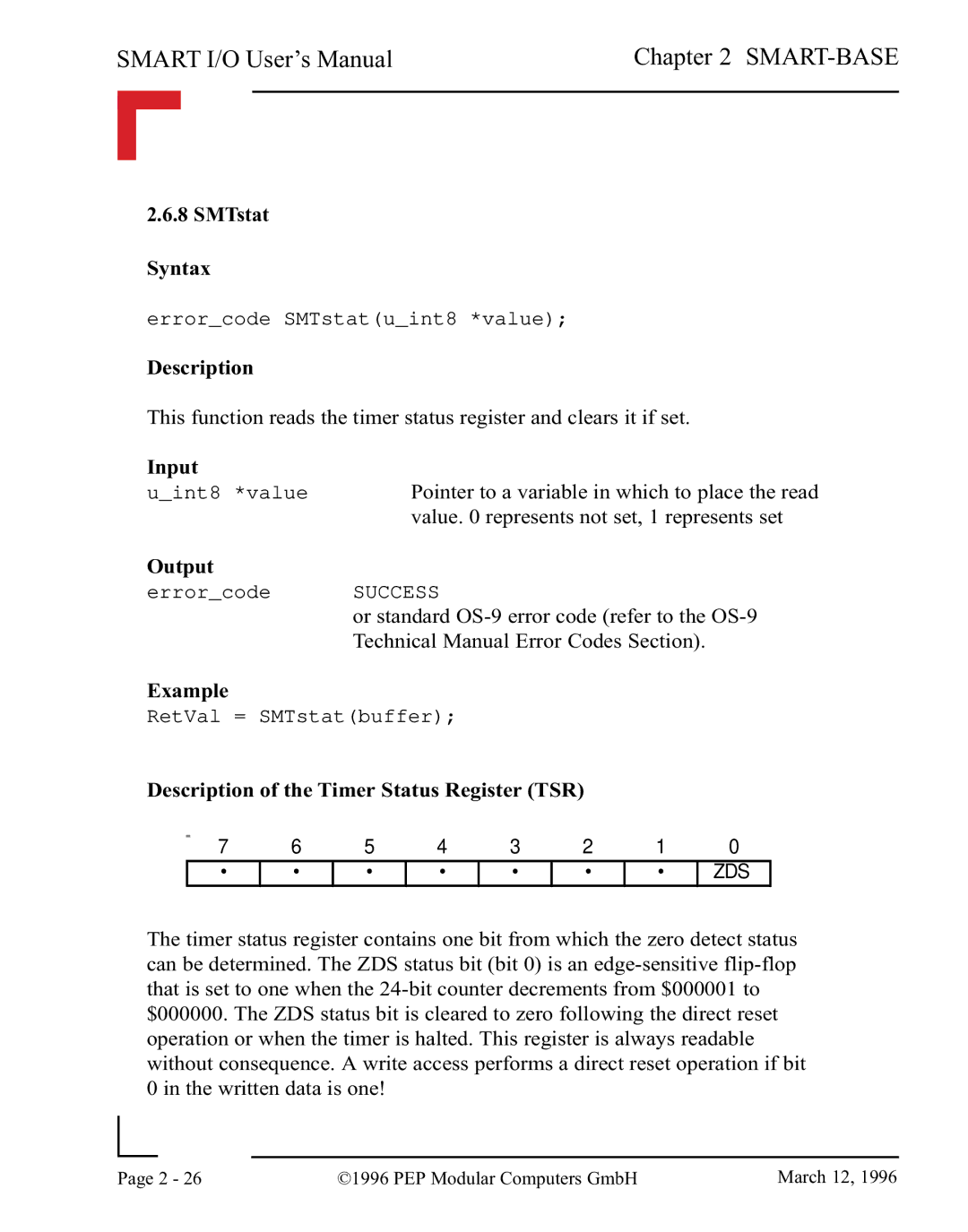

Description of the Timer Status Register (TSR)

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

• | • | • | • | • | • | • | ZDS |

The timer status register contains one bit from which the zero detect status can be determined. The ZDS status bit (bit 0) is an

|

|

|

|

Page | 2 - 26 | ©1996 PEP Modular Computers GmbH | March 12, 1996 |

|

|

|