TX39 Family Core Architecture

Page

Toshiba

Contents

EPC Exception Program Counter register

Memory location of exception vectors

Appendix a Instruction Set Details

Coprocessor Unusable exception

Bus Interface Unit Bus Controller / Write Buffer

227

Bus request and bus grant 227 Cache snoop 228

229

230

Architecture

Architecture

Features

Introduction

High-performance Risc techniques

Low power consumption

Signal notation

Notation Used in This Manual

Mathematical notation

Data notation

Architecture

Architecture

Overview

Registers

CPU registers

CP0 registers

Reserved †

Exception program counter

Instruction Set Overview

Operation code 6 bits

Source register 5 bits

Destination register 5 bits

Load/store

Computational

Jump/branch

Coprocessor

Computational Instructions

ALU Immediate

ALU 3-operand, register type

Multiply/Divide

Jump/Branch Instructions

Coprocessor Instructions

Special Instructions

Special Instruction

CP0 instructions Instruction Description CP0 Instructions

Data Formats and Addressing

Big endian and little endian formats

Architecture

Byte addresses of a misaligned word

Pipeline Processing Overview

User mode

Kernel mode

Memory Management Unit MMU

1 R3900 Processor Core operating modes

Direct segment mapping

Kuseg

Kseg0

Kseg1

Address mapping

Architecture

Instruction Set Overview

Instruction Formats

Instruction Notation

Byte specifications for load and store instructions

Load and Store Instructions

Base Offset

Sync

Computational Instructions

NOR

SLLV, SRLV, Srav Instruction Format and Description

MFHI, Mflo Instruction Format and Description

MTHI, Mtlo Instruction Format and Description

Architecture

Jump/Branch Instructions

Jump instructions

Instruction Format and Description

Instruction in the delay slot is executed during the jump

10. Branch instructions

Architecture

Special Instructions

11. Special instructions

Coprocessor Instructions

COPz Instruction Format and Description

BCzT, BCzF Instruction Format and Description

Architecture

Restore From

System Control Coprocessor CP0 Instructions

13. System control coprocessor CP0 instructions

Cache Instruction Format and Description

Pipeline Architecture

Delay Slot

Delayed load

Delayed branching

Nonblocking Load Function

Nonblocking load function

Divide Instruction DIV, Divu

Streaming

Memory Management Unit MMU

R3900 Processor Core Operating Modes

Direct Segment Mapping

Internal MMU virtual address space

Kuseg

512MB

Exception Processing

Utlb

TLBL2

Exception Processing Registers

Cause register

Status register

Cache register

Cause register register no.13

Bits Mnemonic Field name Description

Read/Write

ExcCode field

Mnemonic Cause

Status register register no.12

Bits

Field name Description

Read

Status register 1/2

Bits Mnemonic Field name Description Value on Read

KUc/KUp/KUo Kernel/User mode current/previous/old

IEc/IEp/IEo Interrupt Enable current/previous/old

NmI Non-maskable Interrupt

IntMask Interrupt Mask

Cache register register no.7

Cache register

DALc/DALp/DALo Data Cache Auto-Lock current/previous/old

IAL DAL

Shows how the RFE instruction works

BadVAddr Bad Virtual Address register register no.8

PRId Processor Revision Identifier register register no.15

Config Configuration register register no.3

21-19

10. Config register2/2

Exception Details

Address Error exception ∙ Causes

∙ Exception mask

∙ Applicable instructions

∙ Processing

Breakpoint exception ∙ Cause

∙ Servicing

Bus Error exception ∙ Causes

Architecture

Coprocessor Unusable exception ∙ Cause

Interrupts ∙ Cause

Overflow exception ∙ Cause

Reserved Instruction exception ∙ Cause

Reset exception ∙ Cause

System Call exception ∙ Cause

Non-maskable interrupt ∙ Cause

Architecture

Priority of Exceptions

Return from Exception Handler

Priority of Exceptions Exception Mnemonic

Architecture

Caches

Instruction Cache

Data cache configuration

Data Cache

Lock bit setting

Lock function

Operation during lock

Lock bit clearing

Auto-lock bits

Cache Test Function

Cache disabling

Cache flushing

Example

Cache Refill

Cache refill

Cache Snoop

Architecture

Debugging Functions

System Control Processor CP0 Registers

PRId Processor revision ID Debug †† Debug exception control

Depc ††

DBD Debug Branch Delay

DM Debug Mode 0 at reset

Debug register register no.16

BsF Bus Error Exception Flag

SSt Single at reset

NIS Non-maskable Interrupt Status

OES Other Exceptions Status

Debug Exceptions

DSS bit

Types of debug exceptions

Debug Single Step DSS

Branching to a debug exception handler

Ii Debug exception handler execution

Iii Return from a debug exception handler

Executing a Deret instruction

Exception priorities

Details of Debug Exceptions

Single Step exception ∙ Cause

∙ Exception masking

∙ Instruction causing this exception

Debug Breakpoint exception ∙ Cause

Architecture

Appendix a Instruction Set Details

Instruction Classes

Instruction Formats

Instruction Notation Conventions

Twos complement division

Bitwise logical XOR operation

Examples of Instruction Notation

Table A-2. Common Load/Store Functions

Function Meaning

Word access 32 bits

Triplebyte access 24 bits

Halfword access 16 bits

Byte access 8 bits

Jump and Branch Instructions

ADD

Addi

Addiu

Addu

Rd, rs, rt

Andi

BCzF

Operation Code Bit Encoding

BCzFL

111

BCzT

113

BCzTL

115

BEQ

Beql

Bgez

Bgezal

Bgezall

Bgezl

Bgtz

Bgtzl

Blez

Blezl

Bltz

Bltzal

Bltzall

Bltzl

BNE

Bnel

Break

Bit# Cache Name

Data

Bit# Cache Operation Description Name

CFCz

COPz

COPz

CTCz

Deret

DIV

Divu

Jump

JAL

Jalr

JR rs

LB rt, offsetbase

LBU

LH rt, offsetbase

LHU

LUI

LW rt, offsetbase

LWL

152

LWR

154

Multiply/Add

Maddu

MFC0

MFCz

MFCz

MFCz

Mfhi

Mflo

MTC0

MTCz

MTCz

Mthi

Mtlo

Mult

Multu

NOR

Or rd, rs, rt

ORI

RFE

SB rt, offsetbase

Sdbbp

SH rt, offsetbase

SLL

Sllv

SLT

Slti

Sltiu

Sltu

SRA

Srav

SRL

Srlv

SUB

Subu

SW rt, offsetbase

SWL

189

SWR

191

Sync

Syscall

XOR

Xori

OPcode

Special function

COPz rs

COPz rt

CP0 Function

Notation

TMPR3901F

200

R3900 Processor Core

On-chip peripheral circuits

Bus interface for ease of system implementation

Low power consumption, optimal for portable applications

Debugging support functions on chip

Maximum operating frequency

Package

Internal Blocks

R3900 Processor Core Clock generator

Bus interface unit bus controller / write buffer

Address protection unit

204

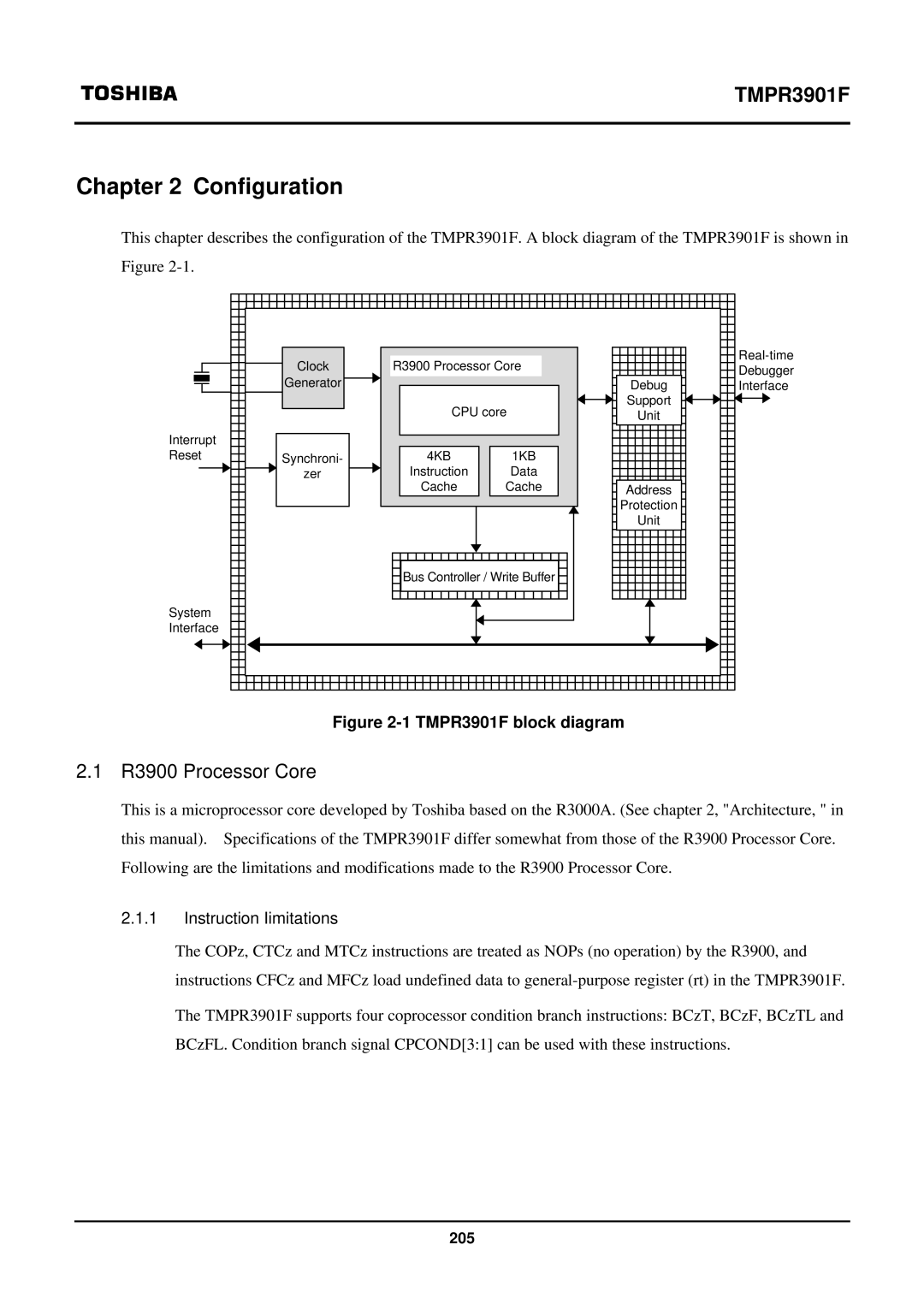

Configuration

R3900 Processor Core

Instruction Iimitations

Clock Generator

Address mapping

Sync NOP

Address Protection Unit

Registers Break Address register BAddr0-1

Break Mask register BMsk0-1

Break Control register BCnt0-1

Break Status register BSts

Memory protection exception

Debug Support Unit

Synchronizer

Register address map

BSts 0xFF00 BAddr0 Bcnt0 BMsk0 BAddr1 Bcnt1 BMsk1

INT* signal synchronization

INT50

NMI* signal synchronization

CPCOND* signal synchronization

CPCOND31

Pins

Enables internal PLL clock

Mode quadruple frequency of crystal oscillator

Halt signal. Indicates that TMPR3901F is in halt mode

Doze signal. Indicates that TMPR3901F is in doze mode

Operations

Clock

∙ Master Clock

∙ Processor Clock

Master clock Processor

System clock

Clock

Read Operation

Single Read

Bus error during a single read operation

Burst Read

Burst read 4 words 1 wait

Bus error in burst read operation 4 words

Write Operation

Single write operation 2 waits

Interrupts

1 NMI

2 INT50

Interrupt

Bus Arbitration

Bus request and bus grant

BUSGNT*L

Reset

Half-Speed Bus Mode

Single read operation in half-speed bus mode

Power-Down Mode

Halt mode

232

Standby Mode

Standby mode PLL stop

Doze Mode

Reduced Frequency Mode