Architecture

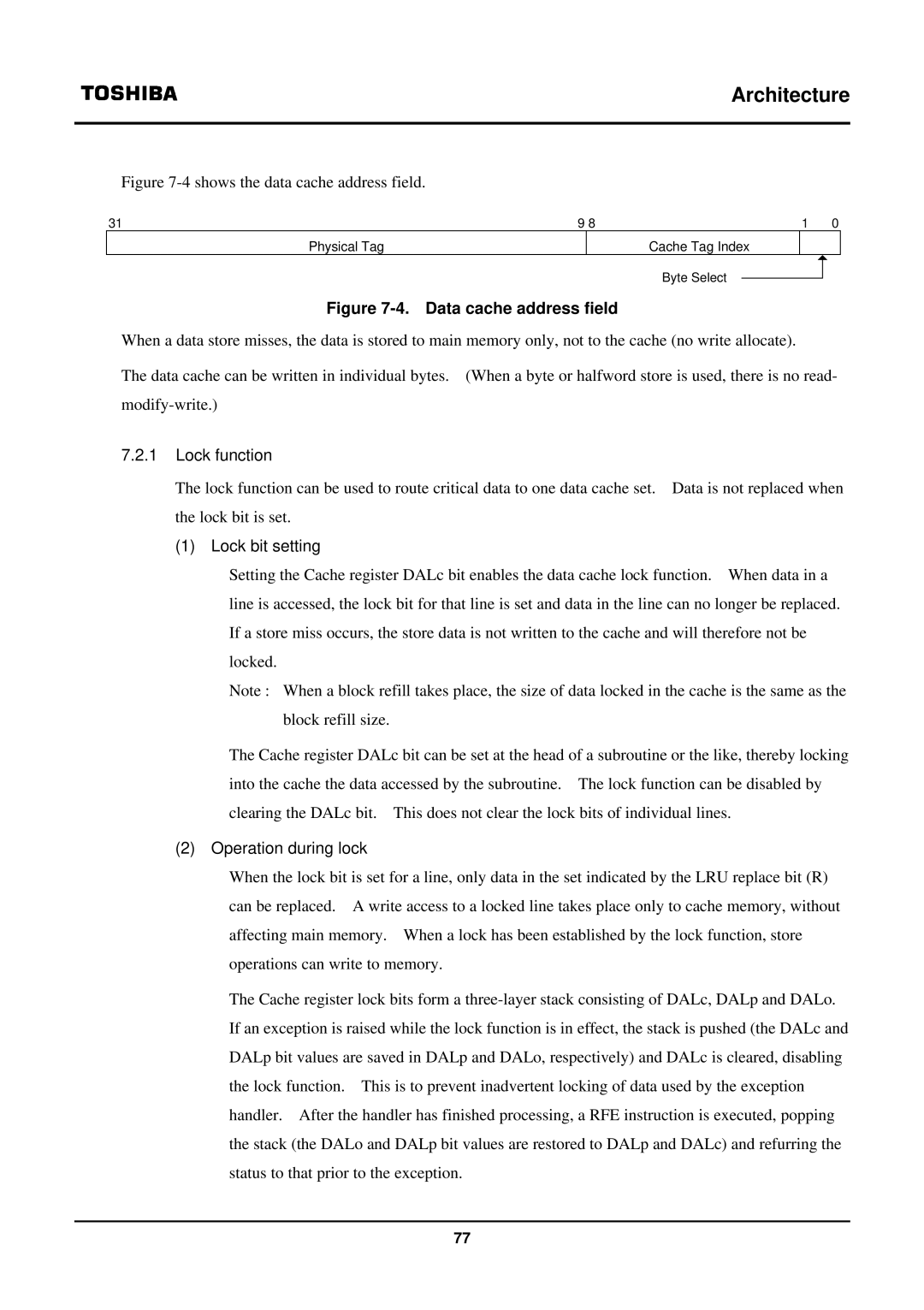

Figure 7-4 shows the data cache address field.

31 | 9 8 | 1 | 0 | ||

Physical Tag |

|

| Cache Tag Index |

|

|

Byte Select

Figure 7-4. Data cache address field

When a data store misses, the data is stored to main memory only, not to the cache (no write allocate).

The data cache can be written in individual bytes. (When a byte or halfword store is used, there is no read-

7.2.1Lock function

The lock function can be used to route critical data to one data cache set. Data is not replaced when the lock bit is set.

(1) Lock bit setting

Setting the Cache register DALc bit enables the data cache lock function. When data in a line is accessed, the lock bit for that line is set and data in the line can no longer be replaced. If a store miss occurs, the store data is not written to the cache and will therefore not be locked.

Note : When a block refill takes place, the size of data locked in the cache is the same as the block refill size.

The Cache register DALc bit can be set at the head of a subroutine or the like, thereby locking into the cache the data accessed by the subroutine. The lock function can be disabled by clearing the DALc bit. This does not clear the lock bits of individual lines.

(2) Operation during lock

When the lock bit is set for a line, only data in the set indicated by the LRU replace bit (R) can be replaced. A write access to a locked line takes place only to cache memory, without affecting main memory. When a lock has been established by the lock function, store operations can write to memory.

The Cache register lock bits form a

77