Architecture

Chapter 3 Instruction Set Overview

This chapter summarizes each of the R3900 Processor Core instruction types in table format and explains each instruction briefly. Details of individual instructions are given in Appendix A.

3.1 Instruction Formats

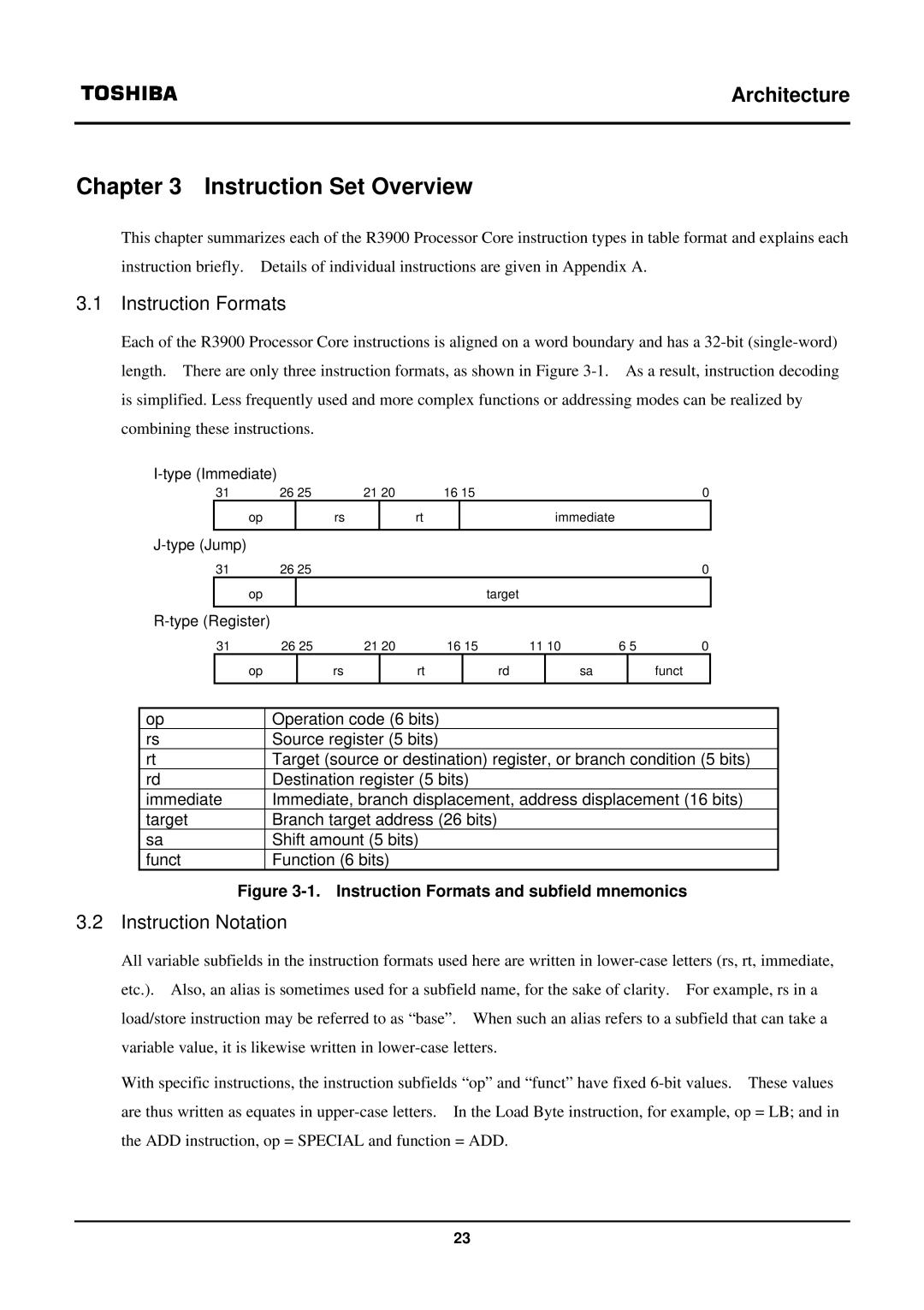

Each of the R3900 Processor Core instructions is aligned on a word boundary and has a

31 | 26 25 | 21 20 | 16 15 | 0 | |||

| op |

| rs |

| rt |

| immediate |

|

|

|

|

|

|

|

|

31 | 26 25 | 0 | |

| op |

| target |

|

|

|

|

31 | 26 25 | 21 20 | 16 15 | 11 10 | 6 5 | 0 |

| ||||||

| op |

| rs |

| rt |

| rd |

| sa |

|

| funct |

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

| ||||

op | Operation code (6 bits) |

|

|

|

|

|

|

|

| ||||

rs | Source register (5 bits) |

|

|

|

|

|

|

|

| ||||

rt | Target (source or destination) register, or branch condition (5 bits) | ||||||||||||

rd | Destination register (5 bits) |

|

|

|

|

|

| ||||||

immediate | Immediate, branch displacement, address displacement (16 bits) | ||||||||||||

target | Branch target address (26 bits) |

|

|

|

|

|

| ||||||

sa | Shift amount (5 bits) |

|

|

|

|

|

|

|

| ||||

funct | Function (6 bits) |

|

|

|

|

|

|

|

| ||||

Figure 3-1. Instruction Formats and subfield mnemonics

3.2 Instruction Notation

All variable subfields in the instruction formats used here are written in

With specific instructions, the instruction subfields “op” and “funct” have fixed

23