TMPR3901F

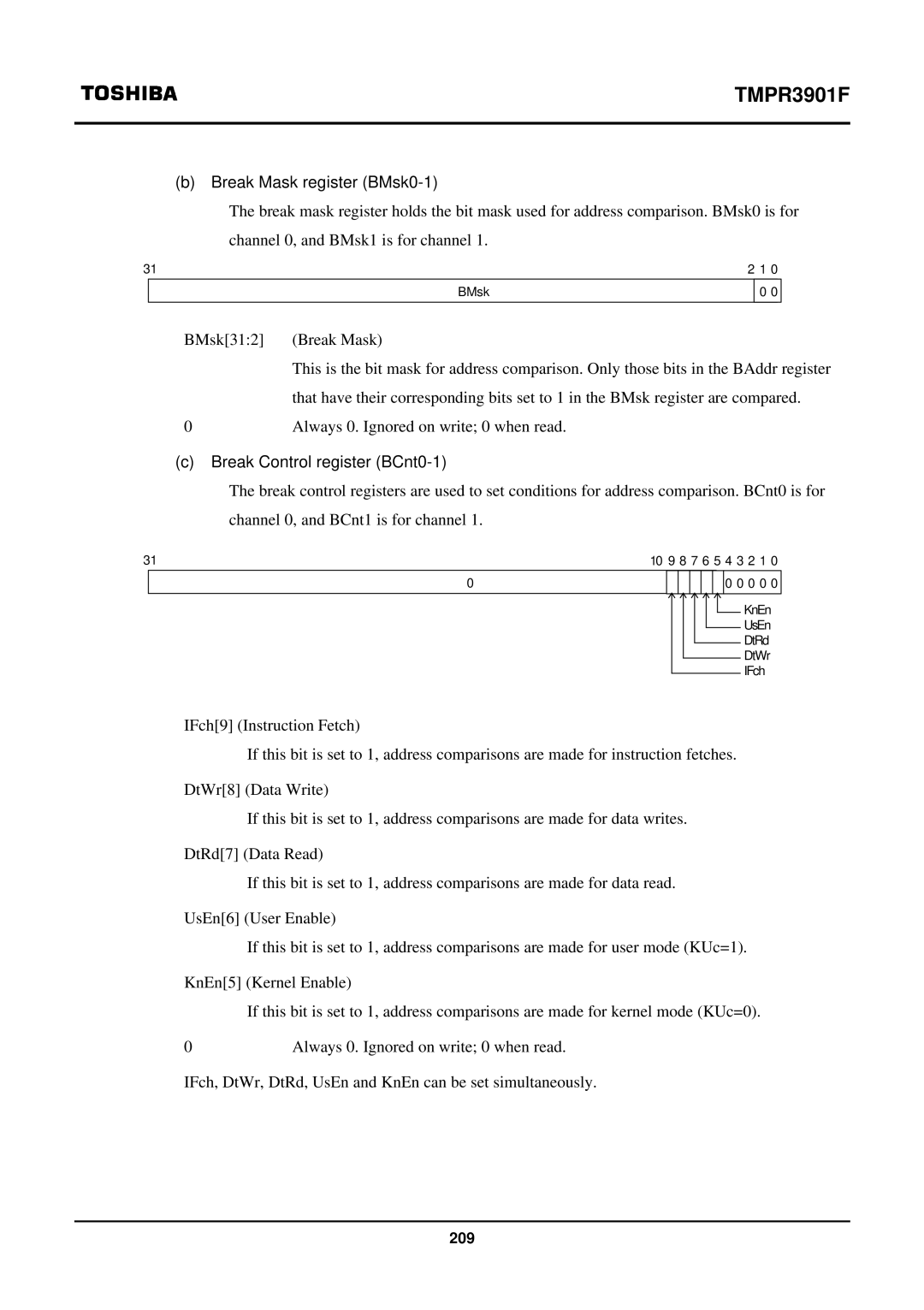

(b) Break Mask register (BMsk0-1)

The break mask register holds the bit mask used for address comparison. BMsk0 is for channel 0, and BMsk1 is for channel 1.

31 |

| 2 1 0 |

| ||

|

| BMsk |

| 0 0 |

|

|

|

|

|

|

|

| BMsk[31:2] | (Break Mask) |

|

|

|

|

| This is the bit mask for address comparison. Only those bits in the BAddr register | |||

|

| that have their corresponding bits set to 1 in the BMsk register are compared. | |||

0 | Always 0. Ignored on write; 0 when read. |

|

|

| |

(c)Break Control register (BCnt0-1)

The break control registers are used to set conditions for address comparison. BCnt0 is for channel 0, and BCnt1 is for channel 1.

31 | 10 9 8 7 6 5 4 3 2 1 0 |

0 | 0 0 0 0 0 |

| KnEn |

| UsEn |

| DtRd |

| DtWr |

| IFch |

IFch[9] (Instruction Fetch)

If this bit is set to 1, address comparisons are made for instruction fetches.

DtWr[8] (Data Write)

If this bit is set to 1, address comparisons are made for data writes.

DtRd[7] (Data Read)

If this bit is set to 1, address comparisons are made for data read.

UsEn[6] (User Enable)

If this bit is set to 1, address comparisons are made for user mode (KUc=1).

KnEn[5] (Kernel Enable)

If this bit is set to 1, address comparisons are made for kernel mode (KUc=0).

0 | Always 0. Ignored on write; 0 when read. |

IFch, DtWr, DtRd, UsEn and KnEn can be set simultaneously.

209